Abstract

Resistive switching memory cross-point arrays with TiN/HfO x /AlO y /Pt structure were fabricated. The bi-layered resistive switching films of 5-nm HfO x and 3-nm AlO y were deposited by atomic layer deposition (ALD). Excellent device performances such as low switching voltage, large resistance ratio, good cycle-to-cycle and device-to-device uniformity, and high yield were demonstrated in the fabricated 24 by 24 arrays. In addition, multi-level data storage capability and robust reliability characteristics were also presented. The achievements demonstrated the great potential of ALD-fabricated HfO x /AlO y bi-layers for the application of next-generation nonvolatile memory.

Similar content being viewed by others

Background

Metal oxide-based resistive random access memory (RRAM) has been extensively studied as one of the most promising candidates for next-generation nonvolatile memory due to the great performances such as fast switching speed, low operating voltage, 3D integration, and good compatibility with CMOS fabrication processes [1-5]. For high-density integration of RRAM array, a cross-point structure with the smallest cell area of 4 F 2 is needed [6,7]. However, the metal oxide-based RRAM devices usually have a large variability [8-10], which hinders application in industries. Thus, it is imperative to seek an effectively technical solution to minimize the variability of RRAM devices.

Various transitional metal oxides such as HfO x [11-13], TaO x [14-16], TiO x [17-19], and ZrO x [20-22] have been reported as resistive switching materials. Among them, HfO x is a superior resistive switching material, which has stable electrical properties, good process repeatability, and small leakage current [23,24]. Based on a previous work [25], an additional buffer oxide layer of AlO y which has a larger oxygen ion migration barrier (E m) will confine the switching in the active oxide, which can improve the uniformity in HfO x -based RRAM devices. Both physical vapor deposition (PVD) and atomic layer deposition (ALD) have been applied to fabricate resistive switching layers. Compared to PVD, the ALD technique has more advantages at constructing uniform, conformal, and ultrathin films, which is a central component for high-density and 3D integration.

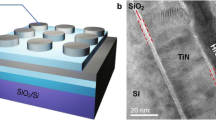

In this paper, the bi-layered HfO x /AlO y films are deposited by ALD as the resistive switching layer of cross-point RRAM array, which shows the precise control of the resistive switching layer in thickness, uniformity, and conformity. The fabricated TiN/HfO x /AlO y /Pt RRAM devices in the cross-point array show excellent performances including low operation voltage (+2/−2 V), sufficient resistance ratio (>10), smaller cycle-to-cycle and device-to-device variations, and high yield (>95%). Meanwhile, multi-level data storage capability, good direct current (DC) endurance (>1,000 cycles), and retention (>104 s at 85°C) properties are demonstrated in the devices.

Methods

The fabrication flow of the HfO x /AlO y -based cross-point RRAM array is schematically shown in Figure 1. Firstly, both the 20-nm Ti adhesion layer and 100-nm Pt bottom electrode (BE) layers were deposited on a SiO2/Si substrate by physical vapor deposition (PVD). Then, the Pt bottom electrode bars were formed by photolithography and lift-off. After that, the 20-nm SiO2 film was deposited by plasma-enhanced chemical vapor deposition (PECVD) to serve as the isolation layer. Different sizes of via holes through the SiO2 isolation layer from 1 × 1 μm2 to 10 × 10 μm2 were formed by reactive ion etching (RIE). Then, 3-nm AlO y and 5-nm HfO x layers were deposited by ALD (Picosun, Masala, Finland) at 300°C, using H2O and trimethylaluminum (TMA)/tetrakis[ethylmethylamino]hafnium (TEMAH) as precursors, followed by a furnace annealing in O2 ambient at 500°C for 30 min. After the 40-nm TiN was sputtered and patterned by photolithography and dry etching to define the top electrode (TE) bars, the contact holes to the pad of the bottom electrode Pt were formed by dry etching. The fabricated array size is 24 × 24, with cross-bar width of 10 μm and pitch along the x and y directions of 20 μm. The pad area of the electrodes is 100 × 100 μm2.

Electrical characterizations were performed using an Agilent B1500A semiconductor parameter analyzer (Agilent Technologies, Inc., Santa Clara, CA, USA). During the measurements, voltage was applied on the TE, while the BE was grounded.

Results and discussion

The resistance values of the fresh devices were usually higher than that of the high-resistance state (HRS) after a RESET process. A two-step forming process was required to activate the RRAM devices and achieve stable resistive switching behaviors. The current–voltage (I-V) curve of the forming process using voltage sweeping is shown in Figure 2. This two-step forming behavior can be attributed to the inhomogeneous distribution of the electric field in HfO x /AlO y layers, which corresponds to the breakdown of HfO x and AlO y layers, respectively. The TE, resistive switching layer, and BE comprise a metal-insulator-metal (MIM) structure, which can be regarded as a plate capacitor with two kinds of dielectrics. According to Gauss’s law, when a voltage is applied across the TE and BE, the electric field intensity in the HfO x layer and AlO y layer can be obtained by the following equations:

Here, εHfO x /εAlO y refers to the dielectric constant of HfO x /AlO y , EHfO x /EAlO y is the electric field intensity in the HfO x /AlO y layer, dHfO x /dAlO y is the thickness of the HfO x /AlO y layer, and V is the value of the applied voltage. By calculating the above equations, the electric field intensity in the AlO y layer is found to be stronger than that in the HfO x layer. Therefore, the dielectric breakdown happens firstly in the AlO y layer at a lower voltage, and then it happens in the HfO x layer at a higher voltage.

A typical DC I-V curve is shown in Figure 3. During SET/RESET operation, bias voltage was applied to the top electrode from 0 to +2/−2 V and then swept back to 0 V, while the bottom electrode was kept grounded. The devices show typical bipolar resistive switching behaviors, with the 1st/50th/100th DC I-V characteristics shown in the figure. The good consistency between the 1st, 50th, and 100th cycles reveals excellent switching cycle uniformity of the RRAM device. Moreover, both switching voltages and HRS/low-resistance state (LRS) distributions were obtained from 100 consecutive DC sweep cycles as shown in Figure 4a,b, respectively. In DC sweep mode, Vset means the voltage at which the current abruptly increases to the compliance current during the set process, and Vreset refers to the voltage at which the current begins decreasing during the reset process. The good cycle-to-cycle uniformity may be attributed to the interfacial effect of the HfO x /AlO y layer [25]. The additional buffer oxide layer of AlO y has a larger oxygen ion migration barrier (E m) and can confine the switching in the active oxide. Among the measured 150 uniformly distributed cells having one 24 × 24 array, only seven RRAM devices cannot switch, which shows the high yield (>95%) of the cross-point array.

A multi-level cell in RRAM is a desirable capability for high-density memory and neuromorphic computing system applications. The multi-level resistive switching behavior of the HfO x /AlO y -based devices can be achieved by adjusting both current compliance during the SET operation and stop voltage during the RESET process, as shown in Figure 5. The LRS resistance can be modulated by SET current compliance possibly due to the modulation of the diameter or number of conductive filament (CF), while the HRS resistance can be controlled by RESET stop voltage possibly due to the modulation of the ruptured CF length [24].

Excellent uniformity of the devices is crucial for array operation, since a large device-to-device variation of resistances or switching voltages may cause READ/WRITE failure. To investigate the device-to-device uniformity, resistance distribution and switching voltage distribution of ten devices were statistically measured and extracted. The results are shown in Figure 6a,b, with solid marks and error bars representing the mean values and standard deviations of 100 consecutive cycles, respectively. It can be found that the HfO x /AlO y devices show good uniformity, which may be ascribed to the precisely controlled resistive switching layer properties in thickness, uniformity, and conformity of the HfO x /AlO y layers by the ALD technique.

Figure 7a exhibits the SET/RESET endurance of 1,000 DC sweep cycles of the HfO x /AlO y -based RRAM devices. The set compliance current was 1 mA, and the reset stop voltage was −2 V. Both LRS and HRS were read at +0.1 V. Data of every cycle was extracted. Though the resistance is not very stable, the resistance ratio is always larger than 10.

In order to confirm the nonvolatility of the devices, time-dependent evolution of the resistance values of both HRS and LRS was monitored at 85°C. The resistance was read every second with a read voltage of 0.1 V. As shown in Figure 7b, both LRS and HRS show no signs of degradation for 104 s.

Conclusions

Excellent resistive switching characteristics of TiN/HfO x /AlO y /Pt RRAM devices in a cross-point array structure have been demonstrated in this work. The devices in the array show excellent cycle-to-cycle and device-to-device switching uniformity, which can be attributed to the precisely controlled HfO x /AlO y bi-layered resistive switching layer by ALD and the effect on the resistive switching behaviors. These superior characteristics of the cross-point RRAM array could be useful for future nonvolatile memory applications.

References

Yoon HS, Baek I-G, Zhao J, Sim H, Park MY, Lee H, et al. Vertical cross-point resistance change memory for ultra-high density non-volatile memory applications. In: Symposium on VLSI Technology Digest of Technical Papers: Jun 15–18 2009. Kyoto, Japan: Piscataway: IEEE; 2009. p. 26–7.

Liu T-Y, Yan TH, Scheuerlein R, Chen Y, Lee JKY, Balakrishnan G, et al. A 130.7 mm2 2-layer 32 Gb ReRAM memory device in 24 nm technology. IEEE J Solid-State Circuits. 2014;49:140–53.

Hsieh M-C, Liao Y-C, Chin Y-W, Lien C-H, Chang T-S, Chih Y-D, et al. Ultra high density 3D via RRAM in pure 28nm CMOS process. In: Proceedings of the 2013 IEEE International Electron Devices Meeting (IEDM): Dec 9–11 2013. Washington, DC: Piscataway: IEEE; 2013. p. 260.

Wong HSP, Lee H-Y, Yu S, Chen Y-S, Wu Y, Chen P-S, et al. Metal-oxide RRAM. Proc IEEE. 2012;100:1951–70.

Waser R, Anono M. Nanoionics-based resistive switching memories. Nat Mater. 2007;6:833–40.

Woo J, Lee D, Cha E, Lee S, Park S, Hwang H. Vertically stacked ReRAM composed of a bidirectional selector and CB-RAM for cross-point array applications. IEEE Electron Device Lett. 2013;34:1512–4.

Park S-G, Yang MK, Ju H, Seong D-J, Lee JM, Kim E, et al. A non-linear ReRAM cell with sub-1μA ultralow operating current for high density vertical resistive memory (VRRAM). In: Proceedings of the 2012 IEEE International Electron Devices Meeting (IEDM): Dec 10–12 2012. San Francisco: Piscataway: IEEE; 2012. p. 501–4.

Guan X, Yu S, Wong HSP. On the switching parameter variation of metal-oxide RRAM—part I: physical modeling and simulation methodology. IEEE Trans Electron Dev. 2012;59:1172–82.

Yu S, Guan X, Wong HSP. On the switching parameter variation of metal oxide RRAM—part II: model corroboration and device design strategy. IEEE Trans Electron Dev. 2012;59:1183–8.

Zhang H, Liu L, Gao B, Qiu Y, Liu X, Lu J, et al. Gd-doping effect on performance of HfO2 based resistive switching memory devices using implantation approach. Appl Phys Lett. 2011;98:042105.

Yu S, Chen HY, Gao B, Kang J, Wong HSP. HfOx-based vertical resistive switching random access memory suitable for bit-cost-effective three-dimensional cross-point architecture. ACS Nano. 2013;7:2320.

Chen YY, Goux L, Clima S, Govoreanu B, Degraeve R, Kar GS, et al. Endurance/retention trade-off on HfO2/metal cap 1T1R bipolar RRAM. IEEE Trans Electron Dev. 2013;60:1114.

Larcher L, Puglisi FM, Pavan P, Padovani A, Vandelli L, Bersuker G. A compact model of program window in HfOx RRAM devices for conductive filament characteristics analysis. IEEE Trans Electron Dev. 2014;61:2668–73.

Ninomiya T, Wei Z, Muraoka S, Yasuhara R, Katayama K, Takagi T. Conductive filament scaling of TaOx bipolar ReRAM for improving data retention under low operation current. IEEE Trans Electron Dev. 2013;60:1384.

Zhuo VYQ, Jiang Y, Zhao R, Shi LP, Yang Y, Chong TC, et al. Improved switching uniformity and low-voltage operation in TaOx-based RRAM using Ge reactive layer. IEEE Electron Device Lett. 2013;34:1130–2.

Maikap S, Jana D, Dutta M, Prakash A. Self-compliance RRAM characteristics using a novel W/TaOx/TiN structure. Nanoscale Res Lett. 2014;9:292.

Yang L, Kuegeler C, Szot K, Ruediger A, Waser R. The influence of copper top electrodes on the resistive switching effect in TiO2 thin films studied by conductive atomic force microscopy. Appl Phys Lett. 2009;95:013109.

Chen YS, Chen B, Gao B, Chen LP, Lian GJ, Liu LF, et al. Understanding the intermediate initial state in TiO2-δ/La2/3Sr1/3MnO3 stack-based bipolar resistive switching devices. Appl Phys Lett. 2011;99:072113.

Kim KM, Choi BJ, Lee MH, Kim GH, Song SJ, Seok JY, et al. A detailed understanding of the electronic bipolar resistance switching behavior in Pt/TiO2/Pt structure. Nanotechnology. 2011;22:254010.

Li Y, Long S, Lv H, Liu Q, Wang Y, Zhang S, et al. Improvement of resistive switching characteristics in ZrO2 film by embedding a thin TiOx layer. Nanotechnology. 2011;22:254028.

Chand U, Huang C-Y, Tseng T-Y. Mechanism of high temperature retention property (up to 200°C) in ZrO2-based memory device with inserting a ZnO thin layer. IEEE Electron Device Lett. 2014;35:1019–21.

Wu M-C, Lin Y-W, Jang W-Y, Lin C-H, Tseng T-Y. Low-power and highly reliable multilevel operation in ZrO2 1T1R RRAM. IEEE Electron Device Lett. 2011;32:1026–8.

Butcher B, Koveshnikov S, Gilmer DC, Bersuker G, Sung MG, Kalantarian A, et al. High endurance performance of 1T1R HfOx based RRAM at low (<20uA) operative current and elevated (150°C) temperature. In: 2011 IEEE International Integrated Reliability Workshop Final Report: Oct 16–20 2011. South Lake Tahoe: Piscataway: IEEE; 2011. p. 146–50.

Lee HY, Chen PS, Wu TY, Chen YS, Wang CC, Tzeng PJ, et al. Low power and high speed bipolar switching with a thin reactive Ti buffer layer in robust HfO2 based RRAM. In: Proceedings of the 2008 IEEE International Electron Devices Meeting (IEDM): Dec 15–17 2008. San Francisco: Piscataway: IEEE; 2008. p. 297.

Yu S, Jeyasingh R, Wu Y, Wong HSP. Understanding the conduction and switching mechanism of metal oxide RRAM through low frequency noise and AC conductance measurement and analysis. In: Proceedings of the 2011 IEEE International Electron Devices Meeting (IEDM): Dec 5–7 2011. Washington, DC: Piscataway: IEEE; 2011. p. 275–8.

Acknowledgements

This work is supported in part by the 973 Program (2011CBA00600) and NSFC Program (61334007, 61421005, 61376084, 61404006).

Author information

Authors and Affiliations

Corresponding author

Additional information

Competing interests

The authors declare that they have no competing interests.

Authors’ contributions

ZC fabricated the cross-point memory arrays with the assistance of FZ, carried out the measurement and analysis, and drafted the manuscript under the instruction of JK, XL, LL, and BG. BC and YZ provided useful suggestions for the layout design. JK supervised the work and finalized the manuscript. All authors read and approved the final manuscript.

Authors’ information

ZC received her B.S. degree from Xidian University, Xi’an, China, in 2012. She is currently pursuing a Ph.D. degree at the Institute of Microelectronics, Peking University, Beijing, China. FZ received his B.S. degree from Xidian University, Xi’an, China, in 2009. He is currently pursuing a Ph.D. degree at the Institute of Microelectronics, Peking University, Beijing, China. BC received his B.S. degree from Sichuan University, Chengdu, China, in 2008. He is currently pursuing a Ph.D. degree at the Institute of Microelectronics, Peking University, Beijing, China. YZ received his B.S. degree from the University of Electronic Science and Technology of China, Chengdu, China, in 2012. He is currently pursuing a M.S. degree at the Institute of Microelectronics, Peking University, Beijing, China. BG received his Ph.D. degree in microelectronics and B.S. degree in physics from Peking University, Beijing, China, in 2013 and 2008, respectively. He currently has a post-doctoral position at the Institute of Microelectronics, Peking University. LL received his Ph.D. degree in materials physics and chemistry from the Institute of Semiconductors, Chinese Academy of Sciences, Beijing, China, in 2005. He is currently an associate professor at the Institute of Microelectronics, Peking University, Beijing. XL received her Ph.D. degree in microelectronics from Peking University, Beijing, China, in 2001. She is currently a professor at the Institute of Microelectronics, Peking University. JK received his Ph.D. degree in solid-state electronics from Peking University, Beijing, China, in 1995. He is currently a professor at the Institute of Microelectronics, Peking University.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made.

The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

To view a copy of this licence, visit https://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Chen, Z., Zhang, F., Chen, B. et al. High-performance HfO x /AlO y -based resistive switching memory cross-point array fabricated by atomic layer deposition. Nanoscale Res Lett 10, 70 (2015). https://doi.org/10.1186/s11671-015-0738-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1186/s11671-015-0738-1