Abstract

A vertical GaN power MOSFET featuring an integrated fin-shaped non-junction diode (FDMOS) is proposed to improve reverse conduction and switching characteristics. Its static and dynamic characteristics are studied and analyzed by Sentaurus TCAD simulation. Compared with the conventional MOSFET (Con. MOS) with a body diode as a freewheeling diode (FWD), the FDMOS uses the integrated fin-shaped diode to reverse conduction, and thus, a low reverse turn-on voltage VON of 0.66 V is achieved, with a decreasing of 77.9%. Moreover, the Qrr of the FDMOS is reduced to 1.36 μC from 1.64 μC of the Con. MOS, without the minority carrier injection. The gate charge (QGD) of the FDMOS is significantly reduced because the fin structure reduces the gate area and transforms some part of CGD to CGS, and thus, a low switching loss is realized. The QGD, the turn-on loss (Eon) and the turn-off loss (Eoff) of the FDMOS are decreased by 56.8%, 33.8% and 53.8%, respectively, compared with those of the Con. MOS. In addition, the FDMOS is beneficial to reduce the parasitic inductance and the total chip area compared with the conventional method of using an externally connected Schottky diode as an FWD.

Similar content being viewed by others

Introduction

GaN-based devices are excellent candidates for power devices due to high critical electric field, high electron mobility and high-temperature operation [1,2,3,4,5]. Many researches focus on lateral high electron mobility transistors (HEMTs) because of its high-density and high-mobility two-dimensional electron gas (2DEG) [6,7,8], which allows high-voltage devices with low on-resistance and high switching speed. However, owing to the high-density interface states and high surface electric field (E-field) peak, the lateral HEMTs normally suffer from severe stability and reliability issues [9]. The vertical transistors can make full use of the potential of GaN material for high breakdown voltage [10,11,12].

For practical use of the vertical transistors in topologies of power converters (e.g., buck/boost converters), reverse conduction with low loss is also demanded to release the surplus energy induced by the inductive load [13]. The typical turn-on voltage (VON) of the body diode in Si MOSFET is only 0.7 V, while the typical VON of the GaN PiN diode is close to 3 V [14]. Moreover, the P-i-N diode is bipolar device, and its rise time (tr) and fall time (tf) are very large, owing to the large reverse recovery charge (Qrr) during on/off transition [15, 16]. Using an external anti-paralleled Schottky barrier diode (SBD) as a freewheeling diode (FWD) for reverse conduction is easy to reduce VON. However, the large parasitic inductance is introduced, resulting in the extra power loss and system instability. One solution is the monolithically integration of the SBD. It decreases the number of parasitic components and simplifies packaging [17], but the leakage current in the off-state is a drawback nevertheless.

In this paper, a novel vertical GaN MOSFET with integrated fin-shaped diode (FDMOS) is proposed to improve the reverse conduction characteristic. Compared with the conventional MOSFET (Con. MOS) with a body diode as a FWD, the VON and Qrr of the FDMOS are significantly reduced. In addition, compared with the conventional method of using an externally connected Schottky diode as an FWD, the integrated fin-shaped diode doesn’t occupy the extra chip area and introduce parasitic inductance.

Structure and Mechanism

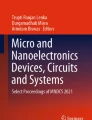

The schematic cross-sectional view of the FDMOS is proposed in Fig. 1a. Compared with the Con. MOS in Fig. 1b, the middle of the planar gate is replaced by a fin-shaped non-junction diode for reverse conduction. In the reverse conduction state, the fin-shaped diode turns on prior to the body diode and thus the reverse turn-on voltage (VON) is greatly reduced. Moreover, without minority carrier injection, reverse recovery charge (Qrr) is reduced. Benefiting from the separated gate, the FDMOS exhibits a low QGD. Simulations are carried out by Sentaurus TCAD. The thickness of the N-drift and the n+ GaN is 7 μm and 0.3 μm, respectively. The thickness of the Al2O3 is 20 nm. The metal work function is 5.15 eV. The doping concentrations of the N-drift (Nd), JFET region and the n+ GaN are 1 × 1016 cm−3, 5 × 1016 cm−3 and 1 × 1021 cm−3. The WJFET and NJFET for the Con. MOS are 1 μm and 5 × 1016 cm−3, respectively. The simulation model used in this paper is similar to the REF [18], which was calibrated by experiment. The physical models include energy bandgap, incomplete ionization, electron and hole mobility, polarization, impact ionization, and radiative and non-radiative recombination. The electron mobility of the fin’s sidewall is assumed to be 13 cm2/V·s in TCAD.

The fin-shaped diode is pinched off at VDS = 0 V because the fin is fully depleted by the work function difference of the MIS structure in the fin sides, as shown in Fig. 2a, c. Therefore, the fin-shaped diode does not affect the forward conduction characteristic. At reverse conduction state, the fin-shaped diode acts as an FWD. With an increasing reverse biased voltage, the depletion area shrinks, and the electron accumulation layer forms along the fin side wall, which provides a reverse current path, as shown in Fig. 2b, f. Figure 2g shows the electron concentration (Ne) along a lateral cutline in the fin channel under different bias voltage VDS. The cutline is shown in Fig. 2e, which is in the middle of the fin. The change of Ne is consistent with the trend in Fig. 2c–f. The Ne > Nd near the sidewall verifies the formation of electron accumulation layer.

Results and Discussion

Figure 3 shows the equivalent circuit of the reverse conduction and reverse conduction characteristic. Figure 3a shows the current path and current density distribution at reverse conduction state. The reverse current in the FDMOS flows through the fin-shaped diode, while the current conduct by the body diode in Con. MOS. According to Fig. 3b, the fin-shaped diode as an FWD exhibits a much lower VON of 0.66 V (@1 A/cm2) in the FDMOS than 2.99 V of the Con. MOS. However, the current capacity (above point O) of the Con. MOS is higher than that of the FDMOS since the Con. MOS works in a bipolar conduction mode, which introduces greater reverse recovery loss nevertheless. The body diode doesn’t conduct because the voltage drop on the body diode for the FDMOS is lower than its turn-on voltage at the reverse conduction state.

Figure 4 shows the analysis of breakdown characteristics. BV is defined as the VDS @ 10−6A/cm2. As shown in Fig. 4a, the FDMOS achieves a hard avalanche breakdown voltage of 1791 V. The fin-shaped diode has a very low reverse leakage current of ~ 10−7 A/cm2 at VDS = − 1600 V, and the switching current ratio (Ion/Ioff) is over 1010. The leakage current and the barrier height (ΦB) satisfy the I ∝ exp(− ΦB/kt) relation. Figure 4b shows the extracted conduction band energy along the middle of fin channel at different VDS values. The width of barrier decreases with the increasing VDS, and the barrier height decreases almost linearly. The holes generated by the avalanche breakdown enter the fin channel region leads to the increase in the fin potential, and thus, the barrier height decreases rapidly. Therefore, the leakage current increases rapidly and the breakdown occurs.

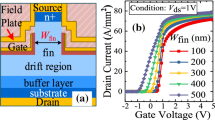

Figure 5 shows the impacts of Lfin and Wfin on ΦB and reverse conduction characteristics for the FDMOS. As shown in Fig. 5a, ΦB decreases with the increase in Wfin and increases with the increase in Lfin because of the increasing overlap of the depletion region. A high ΦB is beneficial to achieving a high breakdown voltage, but it leads to the high VON. In addition, the fin channel mobility is low, and thus, the resistance increases with the increase in Lfin, as shown in Fig. 5b. Considering the trade-off between breakdown characteristics and on-state performance, the optimized Lfin and Wfin is 0.8 μm and 0.2 μm, respectively.

Figure 6 shows the gate charge characteristics of the two devices. The QGD of the FDMOS is 114 nC/cm2, which is far less than 264 nC/cm2 of the Con. MOS. One reason is that the overlap area between the gate and drain is reduced. The other is that the source metal surrounding the fin can effectively shield the gate-drain overlap, and thus, part of the capacitance between gate and drain (CGD) transforms to the capacitance between gate and source (CGS) for the FDMOS.

Figure 7a shows that the FDMOS achieves better reverse recovery characteristics and lower reverse recovery loss. Figure 7b compares the hole distribution of the FDMOS and the Con. MOS during reverse recovery. The FDMOS device is in unipolar mode, and thus, the hole concentration in the drift region is very low, which is far less than n-drift concentration (1 × 1016 cm−3). However, the drift region of the Con. MOS has a high hole concentration due to the minority injection. Compared with the Con. MOS, the FDMOS reduces the Qrr from 1.64 to 1.36 μC, and reduces trr from 170 to 86 ns as shown in Fig. 7a.

Figure 8a shows the test circuit for switching characteristic. The Switch 1 (S1) and the Switch 2 (S2) are the same device, and they can be the proposed FDMOS or the Con. MOS. The gate and the source of the S1 is short-circuited as the FWD diode, and a parasitic inductor Lp = 10 nH is connected with S1 to simulate the overvoltage caused by reverse recovery of the FWD diode. Figure 8b, c shows power dissipation and turn-on/off curves. The tr of the FDMOS and the Con. MOS are 52 ns and 126 ns, respectively. The current rise rate of the FDMOS and the Con. MOS is almost the same, and the voltage drop rate of the FDMOS is much higher than that of the Con. MOS due to the smaller QGD. Therefore, the Eon of the FDMOS reduces by 33.8% in comparison with the Con. MOS. Owing to the low QGD, as shown in Fig. 6, the Eoff of the FDMOS reduces from 11.08 to 5.11 mJ, decreasing by 53.8% in comparison with that of the Con. MOS.

The key process steps have been given out to show that the structure is doable, as shown in Fig. 9. The required GaN epi layer was proposed and fabricated in REF [19]. Firstly, the n-GaN drift region is grown by metalorganic chemical vapor deposition (MOCVD), and the P-GaN region is formed by implantation of Mg ion, as shown in Fig. 9a, b. Then, the top GaN layer is regrown by plasma-MBE. The p-GaN regions are used as the P-base region. Secondly, the fin is formed by Cl2/BCl3-based inductively coupled plasma (ICP) etching, and Al2O3 dielectric is formed by ALD, as shown in Fig. 9d. The oxide etch depth is controlled by a timed photoresist (PR) etch [20]. The mask is photoresist, treated with O2 plasma as shown in Fig. 9e, f. Then the Al2O3 dielectric is etched down by buffered oxide etch (BOE) to expose top n+ surface and the mask is removed, as shown in Fig. 9g, h. Complete FDMOS structure with implanted n+ source/drain, metal electrodes and anode metal is not drawn in Fig. 9.

Key fabrication process flows for the FDMOS. a–c GaN epi layer growth [19]; d ICP etch to form the fin and deposit the Al2O3 dielectric; e–h Expose top n+ surface

Conclusion

In this work, a normally off vertical GaN power MOSFET with an integrated fin-shaped diode is proposed. A unipolar fin-shaped diode realizes a low reverse conduction voltage and a low reverse recovery charge Qrr. Meanwhile, the design also results in a much smaller QGD. Therefore, the FDMOS reduces the reverse turn-on voltage by 77.9% compared with that of the Con. MOS. The QGD, Eon and Eoff of the FDMOS are decreased by 56.8%, 33.8% and 53.8% respectively, compared with those of the Con. MOS. The integration of the fin-shaped diode eliminates the parasitic effect and reduces the total chip area, compared with the conventional method of using an external Schottky diode.

Availability of Data and Materials

All data generated or analyzed during this study are included in this article.

References

Chen KJ, Haberlen O, Lidow A, Tsai CL, Ueda T, Uemoto Y, Wu Y (2017) GaN-on-Si power technology: devices and applications. IEEE Trans Electron Devices 64(3):779–795. https://doi.org/10.1109/TED.2017.2657579

Rupp R, Laska T, Häberlen O, Treu M (2014) Application specific trade-offs for WBG SiC, GaN and high end Si power switch technologies. In: IEDM technical digest, pp 2.3.1–2.3.4. https://doi.org/10.1109/IEDM.2014.7046965

Chow TP, Tyagi R (1994) Wide bandgap compound semiconductors for superior high-voltage unipolar power devices. IEEE Trans Electron Devices 41(8):1481–1483. https://doi.org/10.1109/16.297751

Mishra UK, Parikh P, Wu Y-F (2002) AlGaN/GaN HEMTs—an overview of device operation and application. Proc IEEE 90(11):1022–1031. https://doi.org/10.1109/JPROC.2002.1021567

Ishida M, Ueda T, Tanaka T, Ueda D (2013) GaN on Si technologies for power switching devices. IEEE Trans Electron Devices 60(10):3053–3059. https://doi.org/10.1109/TED.2013.2268577

Zheng Z, Zhang L et al (2021) Gallium nitride-based complementary logic integrated circuits. Nat Electron 4:595–603. https://doi.org/10.1038/s41928-021-00611-y

Ma J, Matioli E (2017) High performance Tri-gate GaN power MOSHEMTs on silicon substrate. IEEE Electron Device Lett 38(3):367–370. https://doi.org/10.1109/LED.2017.2661755

Ma J, Matioli E (2017) Slanted tri-gates for high-voltage GaN power devices. IEEE Electron Device Lett 38(9):1305–1308. https://doi.org/10.1109/LED.2017.2731799

Vetury R, Zhang NQ, Keller S, Mishra UK (2001) The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs. IEEE Trans Electron Devices 48(3):560–566. https://doi.org/10.1109/16.906451

Sun M, Zhang Y, Gao X, Palacios T (2017) High performance GaN vertical fin power transistors on bulk GaN substrates. IEEE Electron Device Lett 38:509–512. https://doi.org/10.1109/LED.2017.2670925

Ji D, Laurent MA, Agarwal A, Li W, Mandal S, Keller S, Chowdhury S (2017) Normally OFF trench CAVET with active Mg-doped GaN as current blocking layer. IEEE Trans Electron Devices 64:805–808. https://doi.org/10.1109/TED.2016.2632150

Shibata D, Kajitani R, Ogawa M, Tanaka K, Tamura S, Hatsuda T, Ishida M, Ueda T (2016) 1.7 kV/1.0 mΩcm2 normally-off vertical GaN transistor on GaN substrate with regrown p-GaN/AlGaN/GaN semipolar gate structure. In: IEEE international electron devices meeting (IEDM), pp 10.1.1–10.1.4. https://doi.org/10.1109/IEDM.2016.7838385

Lei J, Wei J, Tang G, Qian Q, Hua M, Zhang Z, Zheng Z, Chen KJ (2017) An interdigitated GaN MIS-HEMT/SBD normally-off power switching device with low ON-resistance and low reverse conduction loss. In: IEEE international electron devices meeting (IEDM), pp 603–12. https://doi.org/10.1109/IEDM.2017.8268456

Xinbo Z, Xu Z, Xing L et al (2016) Fully vertical GaN p-i-n diodes using GaN-on-Si Epilayers. IEEE Electron Device Lett 37(5):636–639. https://doi.org/10.1109/LED.2016.2548488

Qi M, Nomoto K, Zhu M et al (2015) High breakdown single-crystal GaN p-n diodes by molecular beam epitaxy. Appl Phys Lett 107:232101. https://doi.org/10.1063/1.4936891

Fu H, Huang X, Chen H, Z, et al (2017) Ultra-low turn-on voltage and on-resistance vertical GaN-on-GaN Schottky power diodes with high mobility double drift layers. Appl Phys Lett 111:152102. https://doi.org/10.1063/1.4993201

Liu C, Abdul Khadar R, Matioli E (2018) Vertical GaN-on-Si MOSFETs with monolithically integrated freewheeling schottky barrier diodes. IEEE Electron Device Lett 39(7):1034–1037. https://doi.org/10.1109/LED.2018.2841959

Sabui G, Parbrook PJ, Arredondo-Arechavala M et al (2016) Modeling and simulation of bulk gallium nitride power semiconductor devices. AIP Adv 6(5):055006. https://doi.org/10.1063/1.4948794

Chowdhury S, Wong MH, Swenson BL et al (2012) CAVET on bulk GaN substrates achieved with MBE-regrown AlGaN/GaN layers to suppress dispersion. IEEE Electron Device Lett 33(1):41–43. https://doi.org/10.1109/LED.2011.2173456

Zhang Y, Sun M, Piedra B et al (2017) 1200 V GaN vertical fin power field-effect transistors. In: IEEE international electron devices meeting (IEDM). https://doi.org/10.1109/IEDM.2017.8268357

Acknowledgements

Not applicable.

Funding

This work was supported by the National Natural Science Foundation of China under Grant U20A20208 and 61874149, the Outstanding Youth Science Foundation of China under Grant 2018-JCJQ-ZQ-060, and the stable support project for the Institutes of Basic Scientific Research 1902N261.

Author information

Authors and Affiliations

Contributions

TS conceived and performed the simulations and the data analysis. XL supervised this work. All authors discussed the results and contributed to the final manuscript. The authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Ethics Approval and Consent to Participate

Not applicable.

Consent for Publication

Not applicable.

Competing interests

The authors declare that they have no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Sun, T., Luo, X., Wei, J. et al. Vertical GaN Power MOSFET with Integrated Fin-Shaped Diode for Reverse Conduction. Nanoscale Res Lett 17, 78 (2022). https://doi.org/10.1186/s11671-022-03717-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1186/s11671-022-03717-0