Abstract

In this study, the physical and electrical characteristics of Al2O3/La2O3/Al2O3/Si stack structures affected by the thickness of an Al2O3 barrier layer between Si substrate and La2O3 layer are investigated after a rapid thermal annealing (RTA) treatment. Time of flight secondary ion mass spectrometry (TOF-SIMS) and X-ray photoelectron spectroscopy (XPS) tests indicate that an Al2O3 barrier layer (15 atomic layer deposition (ALD) cycles, approximately 1.5 nm) plays an important role in suppressing the diffusion of silicon atoms from Si substrate into the La2O3 layer during the annealing process. As a result, some properties of La2O3 dielectric degenerated by the diffusion of Si atoms are improved. Electrical measurements (C-V, J-V) show that the thickness of Al2O3 barrier layer can affect the shift of flat band voltage (V FB) and the magnitude of gate leakage current density.

Similar content being viewed by others

Background

Microelectronics technology has developed in accordance with Moore’s law for many years. The performance of metal-oxide-semiconductor field-effect transistor (MOSFET) has been improving with the downscaling of feature size. However, in sub-45-nm complementary metal oxide semiconductor (CMOS) technology, the scaling of SiO2 gate dielectric thickness leads to an unacceptable gate leakage current, which affects the reliability of the device and causes an increase in static power dissipation. Therefore, new kinds of dielectric materials with high permittivity are needed to replace the traditional SiO2 gate dielectric to obtain a smaller equivalent oxide thickness (EOT) in the CMOS industry [1,2]. Presently, the use of HfO2 (k ~ 13 to 20) as the gate dielectric in the high-k/metal gate structure has been successfully applied to MOSFET fabrication and is gradually replacing the traditional SiO2/poly-Si gate structure [3]. Nevertheless, further downscaling trend makes the use of HfO2 as gate dielectric in the CMOS technology encounter a bottleneck. During the past two decades, rare earth oxides (Y2O3, La2O3, Nd2O3, etc.) used as alternative gate dielectric materials have been extensively studied [4]. In particular, due to its high k value (approximately 27) and large band gap (approximately 5.3 eV), lanthanum oxide (La2O3) is considered as one of the most promising alternative for HfO2 to achieve a more aggressive downscaling of the EOT [5]. But disadvantages of La2O3 have also been reported, such as hygroscopicity and affinity for silicon atoms [6]. Al2O3 has also been used as high-k gate dielectric material in the early stage, but its further development is limited because of the low k value (8 to 10). However, the combination of Al2O3 and La2O3 results in an improvement in the characteristics of the films used as the gate dielectric. For example, when the La2O3 layer is in situ capped with an Al2O3 layer, the absorption of moisture which gives rise to detrimental effects on the dielectric films such as increased surface roughness and deterioration of the permittivity can be suppressed [7]; in addition, as a compound of Al2O3 and La2O3, LaAlO3 (LAO) has a nearly high k value (25 to 27) as La2O3 while providing a high immunity against moisture absorption and a preferable thermal stability [8] during the annealing process.

It turns out that an interfacial layer (IL) which exhibits a La-silicate composition is unavoidably formed between the La2O3 film and Si substrate. Moreover, in the conventional gate first process with a high-temperature annealing treatment, the diffusion of Si atoms from the substrate into the dielectric results in the formation of undesirable low-permittivity silicates in the films. Both of the two phenomena mentioned above can especially be observed in low-temperature deposited films in which the existence of large amounts of defects and disordered chemical bonds may enhance the diffusion of oxygen and Si atoms and lead to a degradation of the EOT value [9]. Atomic layer deposition (ALD) is a typically low-temperature deposition method, but its self-limited surface reaction mechanism makes the films deposited by ALD have some outstanding properties such as atomic scale thickness controllability, fine uniformity, and excellent conformality [10]. Regarding this, ALD is considered as one of the most appropriate way to produce high-quality high-k gate dielectric. In this study, we prepared Al2O3/La2O3/Al2O3 gate stacks by ALD to circumvent the hygroscopicity and diffusion-related problems of La2O3. A thickness-varied Al2O3 layer was deposited between La2O3 layer and Si substrate as a barrier layer, and its effects on the physical and electrical characteristics of the films were investigated.

Methods

Al2O3/La2O3/Al2O3 gate stacks (S1 ~ S4) were deposited on p-type Si (100) wafers using an atomic layer deposition reactor (Picosun R-200, Espoo, Finland). The wafers were treated with a diluted HF solution to remove the native SiO2 before deposition. La(i-PrCp)3 and TMA were used as the La and Al precursor while O3 was used as the oxidant. Under the deposition temperature of 300°C, for La2O3, a linear relation with a growth rate of approximately 0.85 Å/cycle is obtained, and the steady-state growth rate of Al2O3 films is approximately 0.93 Å/cycle. The fabricated nanolaminate (Al2O3/La2O3/Al2O3) films were annealed at 700°C for 1 min in N2 ambient. Film thicknesses were measured by Woollam M2000D (Woollam Co. Inc., Lincoln, NE, USA) spectroscopic ellipsometry (SE). Cross-sectional high-resolution transmission electron microscopy (HRTEM) performed with the [100] direction [11] of the Si substrate was used to observe the microstructures of the gate stacks. The bonding structures and chemical quantitative composition of the films were examined by X-ray photoelectron spectroscopy (XPS) and time of flight secondary ion mass spectrometry (TOF-SIMS). The electrical properties of the films were measured using a metal-insulator-semiconductor (MIS) capacitor structure. Metal gate (160 nm Au/20 nm Ni) with a diameter of 300 μm was deposited by magnetron sputtering through a shadow mask, and Al was sputtered as the back contact metal, followed by annealing in forming gas ambient at 400°C for 20 min. The capacitance-voltage (C-V) and leakage current density-voltage (J-V) measurements were carried out using a Keithley 590 C-V analyzer (Keithley Instruments, Cleveland, OH, USA) and HP 4156B instrument (Hewlett-Packard Development Company, L.P., Palo Alto, CA, USA). The flat band voltages (V FB) and EOT of the capacitors were extracted from the simulation software named Hauser NCSU CVC program [12] taking into account of quantum-mechanical effects.

Results and discussion

Figure 1 shows the schematic structure of Al2O3/La2O3/Al2O3 gate stacks discussed in this paper. The thickness of La2O3 layers in samples S1 ~ S4 is 5 nm, and all the samples are in situ ALD-capped with a 2-nm Al2O3 layer. The thickness of the Al2O3 barrier layer between La2O3 layers and Si substrate is tuned by varying the number of ALD cycles, which is 0, 5, 10, and 15 cycles for samples S1 ~ S4 separately. Table 1 shows the total thickness of the as-grown and annealed samples measured by spectroscopic ellipsometry (SE). It is reported that La2O3 films are easily hydrated, but in this work, the existence of capping Al2O3 layer suppresses the hydration reaction during the rapid thermal annealing (RTA) process, and as a result, the thickness of each sample does not increase too much after the annealing treatment. However, sample S1 shows a thicker increment about 0.4 nm when compared with the other three samples, which indicates a thicker interfacial layer formation in sample S1.

Figure 2 shows the O 1s XPS spectra and their deconvolution results for the RTA treated Al2O3/La2O3/Al2O3 gate stacks. C 1s peak from adventitious carbon at 284.6 eV [13] was used as an internal energy reference during the analysis. The O 1s XPS spectra consists of four peaks, which are (I) La-O-La (approximately 529.3 eV), (II) La-O-Si (approximately 530.4 eV), (III) Al-O (approximately 531.6 eV), and (IV) Si-O-Si (approximately 532.6 eV) [14]. Among the four deconvoluted peaks, peak I and peak III come from the deposited La2O3 and Al2O3 layer; peak II and peak IV are attributed to SiOx and La-silicate, which indicate the formation of interfacial layer and silicate in the films caused by the diffusion of oxygen and Si atoms during the annealing process [15]. By contrast, we can find out that the intensity of peak II and peak IV corresponding to La-O-Si and Si-O-Si is reduced from samples S1 to S4, respectively. The decreasing trend of peak II and peak IV suggests that, on the one hand, in sample S1 without an Al2O3 barrier layer, Si diffusion into the La2O3 layer is enhanced during a thermal treatment, resulting in a favorable silicate formation through the film and the interface; on the other hand, to some extent, a uniform and dense Al2O3 barrier layer (approximately 1.5 nm) in sample S4 produced by 15 cycles of ALD deposition suppresses the formation of IL and prevents the diffusion of Si atoms, resulting in a silicate formation decrease. In order to study this phenomenon more clearly, cross-sectional HRTEM and time of flight secondary ion mass spectrometry (TOF-SIMS) measurements were applied to samples S1 and S4.

O 1s XPS spectra of Al 2 O 3 /La 2 O 3 /Al 2 O 3 gate stacks shown in Table 1 .

With the deposition method of ALD, different from the LaLuO3/Si stack, in which a sharp interface is observed [16], the IL seems hardly to be avoided in the La2O3/Si stack because of the affinity for silicon atoms of La2O3, especially after a high-temperature RTA treatment. The cross-sectional HRTEM images for annealed samples S1 and S4 are displayed in Figure 3. Both of the films exhibit an amorphous structure up to an annealing temperature of 700°C [17]. Compared with Figure 3b, a thicker amorphous transition region about 2.5 nm between the deposited film and Si substrate is observed in Figure 3a, indicating a thicker IL formation in sample S1. Figure 4 shows the TOF-SIMS depth profiles of OH−, Al+, Si+, La+, and SiO3 − clusters acquired for samples S1 and S4. The intensity of the signals is dealt with normalization method, and depth values are calibrated by HRTEM results. Large amounts of OH− are detected only at the surface of the films while the internal content is much less and uniformly distributed without a gradient distribution trend suggesting that the diffusion of moisture from air to the films is suppressed by the capping Al2O3 layer. As a result, the moisture absorption of La2O3 layer can be neglected in the Al2O3/La2O3/Al2O3 gate stacks [7]. The intensity of Si+ in sample S4 is at least an order magnitude less than that in sample S1, which suggests that the deposited Al2O3 barrier layer (15 cycles) in sample S4 indeed suppresses the diffusion of Si atoms from the Si substrate into the La2O3 layer during the thermal process, in good agreement with the XPS results. Due to the formation of pinholes in the Al2O3 barrier layer during the 700°C RTA treatment [18], the diffusion of Si atoms is not completely suppressed. HRTEM analysis reveals the existence of a thicker IL in the sample without an Al2O3 barrier layer, and now this result can be further confirmed from the intensity of SiO3 − signals which indicate the presence of a SiOx-like component existing in the region of the nanolaminate/substrate interface. Finally, the depth profiles of Al+ and La+ suggest a serious interdiffusion of La2O3 and Al2O3 layers in the Al2O3/La2O3/Al2O3 gate stacks. This result explains the difficulty in distinguishing the borderlines between La2O3 and Al2O3 layers in Figure 3.

Cross-sectional HRTEM images of annealed samples S1 and S4 shown in Table 1 . (a) Sample S1. (b) Sample S4.

TOF-SIMS depth profiles of annealed samples S1 and S4 shown in Table 1 .

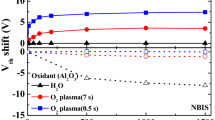

Figure 5 shows the C-V curves and V FB shifts for the Al2O3/La2O3/Al2O3 gate stacks. The EOTs of samples S1 ~ S4 extracted by NCSU CVC program are 4.62, 3.82, 3.85, and 3.28 nm, then the k values can be figured out as 7.3, 8.9, 9.1, and 11.3, respectively. For sample S1, the enhanced diffusion of oxygen and Si atoms during the annealing process owing to the absence of Al2O3 barrier layer makes the permittivity lower while the EOT thicker with respect to those of the others. The doping concentration of the Si substrate used in this work is 5.0 × 1015 cm−3, considering the work function difference between Si substrate and Au/Ni metal gate electrode, the ideal V FB can be worked out as −0.06 V. It is believed that the shift of V FB originates from the existence of net oxide charges in the films [19]. The V FB value for sample S1 is −0.16 V. Accordingly, there are positive net oxide charges in sample S1. The V FB value for samples S2 ~ S4 are observed to be 0.05, 0.15, and 0.26 V, respectively. Such V FB shifts suggest the presence of negative net oxide charges induced by the negative fixed charges existing in the Al2O3 barrier layers [20]. Taking the ideal V FB as a reference, a bigger shifting value of V FB is obtained in sample S4 compared with those of sample S2 and sample S3, which means that, in a very thin range, more negative net oxide charges in the Al2O3/La2O3/Al2O3 gate stacks would be generated as the thickness of Al2O3 barrier layer increases.

The effect of Al2O3 barrier layer thickness on the gate leakage current density is shown in Figure 6. At the applied gate voltage of −5 V, the leakage current density of the films are measured to be 5.92 × 10−1, 1.86 × 10−3, 2.32 × 10−4, and 1.79 × 10−4 A/cm2, separately. The current density reduction of sample S4 by three orders or more from sample S1 is achieved. The low gate leakage current characteristic of sample S4 is considered arise from the large band offsets [21] at the nanolaminate/Si interface. Al2O3 has a large band gap of 8.8 eV and high values of conduction band offset (approximately 2.8 eV) and valence band offset (approximately 4.8 eV) with respect to p-type Si substrate [22,23]. Consequently, the addition of an Al2O3 barrier layer contributes to the formation of a higher potential barrier at the fabricated nanolaminate/Si interface than that at the La2O3/Si interface or the SiOx-silicate/Si interface. The high potential barrier formed between the oxide film and the Si substrate results in a weakening of the tunneling effect of electrons and holes in the metal-insulator-semiconductor capacitor. Therefore, the leakage current density decreases with the existence of an Al2O3 barrier layer.

Conclusions

In summary, an Al2O3 barrier layer (15 ALD cycles, approximately 1.5 nm) between the La2O3 layer and Si substrate plays an important role in blocking the diffusion of Si atoms from Si substrate into the La2O3 layer and the diffusion of oxygen in the opposite direction resulting in a decrease in the thickness of IL and the formation of La-silicate in the Al2O3/La2O3/Al2O3 gate stack during the annealing process. In other words, the existence of the Al2O3 barrier layer provides a gate stack with high permittivity and contributes to the achievement of an improved EOT value. The thickness of the Al2O3 barrier layer also affects the electrical characteristics of the fabricated nanolaminates. In a very thin range (0 ~ 15 cycles), Al2O3 barrier layer brings in negative net oxide charges which leads to a positive shift of V FB. In addition, as the thickness of Al2O3 barrier layer increases, gate leakage current is reduced due to the formation of a high potential barrier between the oxide film and Si substrate.

Abbreviations

- ALD:

-

atomic layer deposition

- CMOS:

-

complementary metal oxide semiconductor

- EOT:

-

equivalent oxide thickness

- HRTEM:

-

high resolution transmission electron microscopy

- IL:

-

interfacial layer

- MIS:

-

metal-insulator-semiconductor

- MOSFET:

-

metal-oxide-semiconductor field-effect transistor

- RTA:

-

rapid thermal annealing

- SE:

-

spectroscopic ellipsometry

- TOF-SIMS:

-

time of flight secondary ion mass spectrometry

- XPS:

-

X-ray photoelectron spectroscopy

References

Lee BH, Oh J, Tseng HH, Jammy R, Huff H. Gate stack technology for nanoscale devices. Mater Today. 2006;9(6):32–40.

Saito S, Torii K, Shimamoto Y, Tonomura O, Hisamoto D, Onai T. Remote-charge-scattering limited mobility in field-effect transistors with SiO2 and Al2O3/SiO2 gate stacks. J Appl Phys. 2005;98:113706.

Kawanago T, Suzuki T, Lee Y, Kakushima K, Ahmet P, Tsutsui K, et al. Compensation of oxygen defects in La-silicate gate dielectrics for improving effective mobility in high-k/metal gate MOSFET using oxygen annealing process. Solid-State Electron. 2012;68:68–72.

Kouda M, Suzuki T, Kakushima K, Ahmet P, Iwai H, Yasuda T. Electrical properties of CeO2/La2O3 stacked gate dielectrics fabricated by chemical vapor deposition and atomic layer deposition. Jpn J Appl Phys. 2012;51:121101.

Kim WH, Maeng WJ, Moon KJ, Myoung JM, Kim H. Growth characteristics and electrical properties of La2O3 gate oxides grown by thermal and plasma-enhanced atomic layer deposition. Thin Solid Films. 2010;519:362–6.

Fanciulli M, Scarel G. Rare earth oxide thin film: growth, characterization and applications. Top Appl Phys. 2007;106:1–14.

Lamagna L, Wiemer C, Perego M, Volkos SN, Baldovino S, Tsoutsou D, et al. O3-based atomic layer deposition of hexagonal La2O3 films on Si(100) and Ge(100) substrates. J Appl Phys. 2010;108:084108.

Liu KC, Tzeng WH, Chang KM, Huang JJ, Lee YJ, Yeh PH, et al. Investigation of the effect of different oxygen partial pressure to LaAlO3 thin film properties and resistive switching characteristics. Thin Solid Films. 2011;520:1246–50.

Suzuki M, Nishi Y, Kinoshita A. Gate-first metal-gate/high-k n-MOSFETs with deep sub-nm equivalent oxide thickness (0.58 nm) fabricated with sulfur-implanted schottky source/drain using a low-temperature process. IEEE Trans Electron Dev. 2011;58(11):3674–7.

Wiemer C, Lamagna L, Fanciulli M. Atomic layer deposition of rare-earth-based binary and ternary oxides for microelectronic applications. Semicond Sci Technol. 2012;27:074013.

Schamm S, Coulon PE, Miao S, Vollkos SN, Lu LH, Lamagna L, et al. Chemical/structural nanocharacterization and electrical properties of ALD-grown La2O3/Si interfaces for advanced gate stacks. J Electrochem Soc. 2009;156:H1–6.

Hauser J. NCSU CVC software, version 7.0. Raleigh, USA: Department of Electrical and Computer Engineering, North Carolina State University.

Pelloquin S, Saint-Girons G, Baboux N, Albertini D, Hourani W, Penuelas J, et al. LaAlO3/Si capacitors: comparison of different molecular beam deposition conditions and their impact on electrical properties. J Appl Phys. 2013;113:034106.

Lee B, Park TJ, Hande A, Kim MJ, Wallace RM, Kim J, et al. Electrical properties of atomic-layer-deposited La2O3 films using a novel La formamidinate precursor and ozone. Microelectron Eng. 2009;86:1658–61.

Park TJ, Sivasubramani P, Wallace RM, Kim J. Effects of growth temperature and oxidant feeding time on residual C- and N-related impurities and Si diffusion behavior in atomic-layer-deposited La2O3 thin films. Appl Surf Sci. 2014;292:880–5.

Shen S, Liu Y, Gordon RG, Brillson LJ. Impact of ultrathin Al2O3 diffusion barriers on defects in high-k LaLuO3 on Si. Appl Phys Lett. 2011;98:172902.

Eom D, No SY, Park H, Hwang CS, Kim HJ. Improvement in thermal stability of stacked structures of aluminum nitride and lanthanum oxide thin films on Si substrate. Electrochem Solid-State Lett. 2007;10:G93–6.

Lee WJ, Ma JW, Bae JM, Kim CY, Jeong KS, Cho MH, et al. The diffusion of silicon atoms in stack structures of La2O3 and Al2O3. Curr Appl Phys. 2013;13:633–9.

Kim H, Woo S, Lee J, Kim H, Kim Y, Lee H, et al. The effects of annealing ambient on the characteristics of La2O3 films deposited by RPALD. J Electrochem Soc. 2010;157:H479–82.

Kornblum L, Meyler B, Cytermann C, Yofis S, Salzman J, Eizenberg M. Investigation of the band offsets caused by thin Al2O3 layers in HfO2 based Si metal oxide semiconductor devices. Appl Phys Lett. 2012;100:062907.

Suzuki M. Comprehensive study of lanthanum aluminate high-dielectric-constant gate oxides for advanced CMOS devices. Materials. 2012;5:443–77.

Mönch W. On the band structure lineup at interfaces of SiO2, Si3N4, and high-k dielectrics. Appl Phys Lett. 2005;86:122101.

Liu D, Clark SJ, Robertson J. Oxygen vacancy levels and electron transport in Al2O3. Appl Phys Lett. 2010;96:032905.

Acknowledgements

This research is supported by the National Natural Science Foundation of China (grant no. 61376099 and 11235008) and the Specialized Research Fund for the Doctoral Program of Higher Education (grant no. 20130203130002 and 20110203110012).

Author information

Authors and Affiliations

Corresponding author

Additional information

Competing interests

The authors declare that they have no competing interests.

Authors’ contributions

XW generated the research idea, analyzed the data, and wrote the paper. XW and CxF carried out the experiments and the measurements. SyY and XjF participated in the discussions. HxL has given final approval of the version to be published. All authors read and approved the final manuscript.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made.

The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

To view a copy of this licence, visit https://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Wang, X., Liu, HX., Fei, CX. et al. Silicon diffusion control in atomic-layer-deposited Al2O3/La2O3/Al2O3 gate stacks using an Al2O3 barrier layer. Nanoscale Res Lett 10, 141 (2015). https://doi.org/10.1186/s11671-015-0842-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1186/s11671-015-0842-2