Abstract

We report a first-of-its-kind, unique approach for generating a self-aligned, gate-stacking heterostructure of Ge quantum dot (QD)/SiO2/SiGe shell on Si in a single fabrication step. The 4-nm-thick SiO2 layer between the Ge QD and SiGe shell fabricated during the single-step process is the result of an exquisitely controlled dynamic balance between the fluxes of oxygen and silicon interstitials. The high-quality interface properties of our “designer” heterostructure are evidenced by the low interface trap density of as low as 2–4 × 1011 cm−2 eV−1 and superior transfer characteristics measured for Ge-based metal-oxide-semiconductor field-effect transistors (MOSFETs). Thanks to the very thin interfacial SiO2 layer, carrier storage within the Ge QDs with good memory endurance was established under relatively low-voltage programming/erasing conditions. We hope that our unique self-aligned, gate-stacking heterostructure provides an effective approach for the production of next-generation, high-performance Ge gate/SiO2/SiGe channel MOSFETs.

Similar content being viewed by others

Background

Rapid expansion of functional electronic applications for mobile devices and for embedded integrated circuit systems has driven a strong and immediate demand for high-speed, low-power transistors and nonvolatile memories. There is, of course, the relentless reduction of feature sizes for achieving desired device performance. In addition, alternative channel materials with higher carrier mobilities are being sought after as a possible solution for realizing next-generation complementary metal-oxide-semiconductor (CMOS) devices [1–9]. Among the possible choices for high-mobility channel materials, Ge has emerged as a leading contender to replace its well-established counterpart, Si, for post-CMOS transistors. This is thanks to Ge’s superior carrier transport efficiency and enhanced charge confinement capabilities [8–16]. Despite these advantages, the production of Ge MOS field-effect transistors (MOSFETs) has been hampered, in particular, in situations where high-temperature thermal oxidation processes are involved. The key for implementing Ge MOS structures lies in the growth of high-quality Ge on Si heterostructures. Sufficiently low defect densities [8, 10] coupled with the formation of gate dielectric layers over the Ge with satisfactory interfacial and electrical properties are required [13–16]. Both of the above requirements are extremely challenging. One is because of the large lattice mismatch of 4.2 % that exists between Ge and Si, and the second is the lack of a robust native oxide for Ge. Unlike the relatively stable SiO2, Ge oxide (GeO x ) is water soluble and thermally unstable. Thus, high densities of interface states (D it ) and rough interfaces between the oxide and the Ge are produced, both of which are detrimental for the realization of high-speed Ge MOSFETs.

Recently, we have demonstrated a unique CMOS compatible, self-assembled approach to deliberately grow spherical Ge quantum dots (QDs) of desired sizes. We also place these QDs at desired spatial locations with controlled depths of penetration into Si. This was achieved using the exquisite control available through lithographic nanopatterning and selective oxidation of the nanopatterned SiGe layers [17–20]. Remarkably, such self-aligned heterostructures of SiO2/Ge QD/SiO2/SiGe shell over the Si substrate can be created in a single fabrication step. In this work, we constructed Ge QD MOS capacitors and Ge floating-dot MOSFETs based on this “designer heterostructure” as well as assessed the interfacial properties of Ge QD/SiO2/SiGe channel from both structural and electrical perspectives. Our devices exhibit reasonably low interface trap densities, good switching behavior, and excellent charge storage characteristics.

Methods

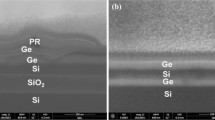

The fabrication starts with tri-layer, sequential low-pressure chemical vapor deposition of 25-nm-thick Si3N4, 70-nm-thick poly-Si0.85Ge0.15, and finally, a capping layer of a 5-nm-thick SiO2 over a Si substrate. The topmost, capping SiO2 and the poly-Si0.85Ge0.15 layers are lithographically defined to create 240-nm diameter, nanocylindrical pillars. The SiGe pillar density is approximately 1 × 109 cm−2 over the buffer Si3N4 layers. Next, the nanopatterned structure is subjected to thermal oxidation at 900 °C within an H2O ambient producing 90-nm diameter, spherical Ge QDs that migrate into the buffer Si3N4 layer [17, 18], as shown in Fig. 1a. Next, an Al top gate (with an area of 75 μm × 75 μm) and substrate electrodes are fabricated over the Ge QD array and the backside of the Si substrate, respectively. A final, forming gas anneal at 400 °C completes the fabrication of the Al-SiO2/Ge QD/SiO2-SiGe MOS capacitors. Additional processes for defining the Al gate and As-doped source/drain (S/D) electrodes are conducted for the fabrication of floating gate MOSFETs. The channel length (L g ) and width (W) are 3 and 50 μm, respectively. High-resolution, cross-sectional transmission electron microscopy (CTEM) and energy dispersive X-ray (EDX) spectroscopy were used to examine the crystallinity, interfacial morphology, and chemical purity of the Ge QD/SiO2/Si heterostructures. Electrical and interfacial properties of SiO2/Ge QD/SiO2/SiGe MOS devices were measured using frequency-dependent capacitance-voltage(C-V) and current–voltage (I-V) characterization over a range of temperatures. Pulse I-V measurements were also conducted to characterize the floating gate memory devices.

a Cross-sectional transmission electron microscopy (CTEM) images as well as EDX elemental b line-scan spectra and c X-ray mapping micrographs of a SiO2/Ge QD/SiO2/SiGe shell heterostructure over the Si substrate. d Selected area diffraction patterns were generated by applying a fast Fourier transform to the local high-resolution CTEM images of the SiGe shell. The interplanar spacing is approximately 3.16 nm, corresponding to Si0.28Ge0.72 {111} planes

Results and Discussion

A core building block for floating gate MOS devices is a heterostructure stack consisting of metal-control oxide-floating gate-tunneling oxide-semiconductor, which is usually achieved via multiple-layer, sequential deposition and patterning. Instead, we have succeeded in generating complex heterostructure stacks of 70-nm-thick SiO2/90-nm Ge QD/4-nm-thick SiO2 over a 20-nm-thick Si0.28Ge0.72 channel in a single, self-organized nanofabrication step. During the high-temperature oxidation of poly-SiGe nanopillars, the Si content in the nanopillar is preferentially oxidized, squeezing the remaining Ge radially inwards to the centers of the oxidized pillars. Further thermal oxidation resulted in the consolidation of the Ge nanocrystallites in each pillar via Ostwald ripening into single spherical Ge QDs. These QDs also simultaneously migrate through the underlying buffer Si3N4 layers and achieve contact with the Si substrate, as shown in Fig. 1a. CTEM-EDX line scanning (Fig. 1b) and mapping (Fig. 1c) examinations confirm the high chemical purity of each Ge QD. Intriguingly, a “cup”-shaped morphology is observed for the Ge QD/Si substrate interface (Fig. 1a). The cup is formed by an approximately 4-nm-thick amorphous interfacial oxide layer, conformal with the QD. Below the interfacial oxide layer, an approximately 20-nm-thick Si1-x Ge x shell is generated within the Si substrate. A substantial amount (x ≈ 0.72) of Ge as estimated from the Raman signal at 414 cm−1 for the SiGe shells formed from the 90-nm Ge QDs [21, 22]. Clear lattice fringes are observed in the high-resolution CTEM micrographs (Fig. 1a). Corresponding selected area diffraction patterns (Fig. 1d), obtained by applying a fast Fourier transform locally to the heterostructure images, confirm the good crystallinity of our self-assembled SiGe shells. The {111} interplanar spacing of ~3.16 nm, suggests that the Si0.28Ge0.72 shell is under a compressive strain of 2.36 %, thus having great promise for possible high-mobility channel p-MOS applications.

As regards the 4-nm interfacial oxide layer separating the Ge QD and the Si substrate, detailed CTEM-EDX examinations reveal that this amorphous interfacial layer is pure SiO2 instead of GeO x . A sharp dip in the Ge X-ray signal coupled with a simultaneous increase in the Si X-ray intensity is observed from the EDX line scans in Fig. 1b. We have previously proposed [18, 20] that this thin, interfacial SiO2 layer between the Ge QD and the SiGe shell is formed by the thermal oxidation of Si interstitials. These interstitials are released from the dissociation of the Si substrate. The SiO2 thickness is consequently determined by a dynamic equilibrium that exists between the concentration of Si interstitials and the external oxygen flux. From a chemical thermodynamics perspective, oxygen clearly prefers to react with the Si interstitials rather than with the Ge because of the large difference in enthalpies of formation for SiO2 (−910.9 kJ/mole) and for GeO2 (−477 kJ/mole) [23]. The clear and abrupt amorphous interfacial SiO2 layer between the QD and the SiGe shell suggests an absence of structural defects near either interface, i.e., the Ge QD/SiO2 interface as well as the SiO2 layer/SiGe shell interface. Therefore, this thermally grown interfacial SiO2 layer over the SiGe shell is believed to possess the advantages of robustness, thermal stability, and superior electrical properties. Essentially similar to SiO2 thermally grown over Si substrates, our Ge QD/SiO2/SiGe heterostructure is amenable for the production of high-performance SiO2/SiGe MOS devices.

Fig. 2a shows the cross-sectional schematic of heterostructured SiO2/Ge QD/SiO2/SiGe n-MOSFET and MOS capacitor. Notably, the channel of studied heterostructured MOS devices consists of SiGe shell channels below the Ge QDs in series with Si channels with no Ge QDs overhead. The gate dielectric layers of SiO2 over the SiGe channel and SiO2/Si3N4 over the Si channel have an equivalent gate oxide thickness (EOT) of approximately 15 and 41 nm, respectively, leading to the SiGe shell being the prime channel that is turned on prior to the parasitic Si channel due to a smaller threshold voltage. Meanwhile, it is a known fact that the interfacial property of Si3N4/Si channel is not as good as that of SiO2/Si. Hence, we believe that our heterostructured SiO2/Ge QD/SiO2/SiGe MOS devices provide a reasonable platform for the assessment of the interfacial properties of Ge QD/SiO2/SiGe channel though extracted interfacial trap density from high-/low-frequency C-V characteristics of MOS capacitors and from the subthreshold slope (S.S.) of transfer (I d -V g ) curves for MOSFETs.

a Cross-sectional schematic of the heterostructured SiO2/Ge QD/SiO2/SiGe n-MOSFET. The gate-stacking region also represents the structural core of the heterostructured MOS capacitor. b Frequency-dependent C-V characteristics of the heterostructured MOS capacitors, where C/C ox represents the normalized capacitance. The inset in b shows the corresponding I-V behavior. c D it values extracted from high-/low-frequency C-V curves in the temperature range of 300–77 K

I-V characteristics were measured for the Al-SiO2/Ge QD/SiO2-SiGe MOS capacitor we fabricated. The typical features of direct tunneling, Fowler-Nordheim tunneling, and hard breakdown, as indicated by regions I, II, and III, respectively, are shown in the inset of Fig. 2b. We also measured a low leakage current density of about 10−9 A/cm2 and a high breakdown electric field (E field) of 8.3 MV/cm. These results verify the electrical robustness of the SiO2/Ge QD/SiO2/SiGe shell heterostructure. Good gate oxide integrity is further evidenced by its frequency-dependent C-V characteristics. Fig. 2b clearly shows that the gate bias controls the surface charge and minority carriers very well at 500–1 MHz with almost no frequency-induced dispersion observable for both n- and p-MOS capacitors. Values for mid-gap D it as low as 2–4 × 1011 cm−2 eV−1 were extracted from the extensive, variable temperature high-/low-frequency C-V characteristics of more than 20 MOS diodes (Fig. 2c). As mentioned previously, the interfacial property of Si3N4/Si channel is no better than that of SiO2/Si, and thereby, the extracted D it values of 2–4 × 1011 cm−2 eV−1 may be overestimated for the solely Ge QD/SiO2/SiGe channel system. Notably, our results are a sharp contrast to the undesirable frequency- and gate bias-dependent capacitance humps/peaks in the weak inversion region usually observed for conventional GeO2/Ge n-MOS capacitors due to the high-interface trap density in the upper half of the bandgap of Ge [11, 15]. Also, our experimental electrical data obviously deviates from the frequency-induced dispersion and stretch out in C-V characteristics as well as E field-dependent Frenkel-Pool conduction in I-V characteristics that are commonly observed for Si3N4/Si MOS capacitors. Both experimental C-V and I-V data are further evidence to support the superior, device-quality interface properties and excellent gate oxide integrity of the SiO2/Ge QD/SiO2/SiGe heterostructure that is applicable for device applications.

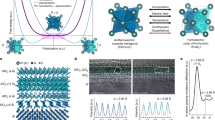

I d -V g of the heterostructured Ge QD/SiO2/SiGe channel nMOSFETs show very low off-state leakage of I off ≅ 10−13 A/μm. A superior on-off current ratio of I on/I off >106 and good switching behavior for S.S. of 195 mV/dec at T = 300 K were also measured (Fig. 3a). This low value of I off leakage as well as the high I on/I off ratio is attributable to the high crystalline quality of the SiGe channel and good interface properties for the thin SiO2 and SiGe channel. The I d -V g characteristics were measured at T = 77–300 K to estimate S.S. from its dependence on temperature. Decreasing the operating temperature from 300 to 77 K results in significant, twofold enhancement of the on-state drive current (Fig. 3b). The S.S. improves from 195 to 105 mV/dec as a result of the suppressed phonon scattering. D it estimated from the S.S. value for n-MOSFETs is approximately 4 × 1011 cm−2 eV−1 at T = 300 K, which is in good agreement with estimates derived from the high-/low-frequency C-V characteristics. As mentioned previously, the conducting channel connecting source and drain indeed consists of the prime SiGe shell in series with the second Si inversion layer that would be sequentially turned on due to the difference in the EOT of gate dielectric layers. It would require a greater gate voltage swing (i.e., larger S.S.) to completely turn on the entire composited channel than the solely SiGe shell. We envisage that significant improvements in S.S. and switching performance are achievable through reducing the parasitic Si channel via shrinking the channel length and increasing the pillar (QD) density within the channel.

Good transfer characteristics such as S.S. of ~100–150 mV/dec and low D it of ~1–5 × 1011 cm−2 eV−1 have been previously reported for the Ge/GeO2 or Ge/GeO2/high-k MOSFETs [9, 11, 14, 15]. However, these characteristics were obtained at the expense of special interfacial treatment prior to and following gate oxidation, such as high-pressure oxidation, two-step oxidation, H2O oxidant pre-pulsing, and post-oxidation annealing. Additionally, all the processing temperatures were constrained to be below 500 °C in order to prevent GeO desorption that severely deteriorates the Ge/dielectric interface and the thermal stability of the Ge MOSFETs [9, 14, 15]. In order to meet the temperature constraint requirement for the production of Ge/GeO2 or Ge/GeO2/high-k MOSFETs, a “gate-last” process is employed. This is because the temperature to activate n-type dopants for source/drain is generally, significantly higher than 500 °C. Finally, in spite of achieving good S.S. and low D it values, the low I on/I off (~104) of Ge/GeO2/high-k MOSFETs is not practicable for low-power device applications because of the high S/D junction leakage due to insufficient activation and rapid diffusion of n-type dopants in Ge [9, 11, 14, 15]. Thus, as compared to the best Ge/GeO2 or Ge/GeO2/high-k MOSFETs, our self-aligned Ge QD/SiO2/SiGe gate-stacking heterostructure possesses comparable interfacial properties (D it ) and subthreshold swing behavior (S.S.). However, the significant advantage of our approach over the conventional state-of-the-art is our fabrication in a single-step, self-organized oxidation process, with the preferred, thermally stable, robust interfacial SiO2 layer rather than the unstable GeO2. Most importantly, our high I on/I off >106 is simultaneously achieved within our designer Ge QD/SiO2/SiGe channel nMOSFETs with S/D junctions that are n+/p Si homojunctions just like in conventional Si MOSFETs.

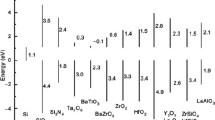

As mentioned above, our heterostructured Ge QD/SiO2/SiGe channel also provides an effective building block for the realization of Ge nanocrystal-based floating gate memories. Thanks to the considerable barrier height adjacent the Ge QD for confining both electrons (~3.2 eV) and holes (~5 eV), significant charge storage stability is achieved within the Ge QDs. This important property was confirmed by counterclockwise and clockwise C-V hysteresis loop measurements in n- and p-MOS capacitors for electron and hole storage, respectively (Fig. 4a). The slopes of C-V curves prior to and following charge injection are nearly unchanged. The nearly indiscernible frequency-induced dispersion and stretch out in C-V characteristics (Fig. 2a), suggests that the charge is primarily stored within the QDs rather than being captured by interface traps or deep traps within Si3N4. The Ge QD, floating gate memory effect is further evidenced by a threshold voltage (V th) shift of ΔV th ~ 0.42 V, which was measured by applying gate voltage pulse under low-voltage programming (+8 V/60 msec) and erasing (−5 V/30 msec) conditions, as shown in Fig. 4b. ΔV th is defined by the difference in gate voltage for these two conditions at a constant drain current value of 1 nA/μm in channel width. Also, thanks to the very thin, 4-nm-thick tunneling oxide, our Ge QD floating gate memory allows low-voltage programming and erasing at +8 and −5 V, respectively. These voltages are almost one half of the corresponding voltages required for state-of-the-art floating gate memory devices [24–26] and definitely very desirable from a reliability perspective. A good memory endurance of more than 105 cycles with negligible ΔV th degradation is measured for our Ge QD devices (Fig. 4c) under the programming/erasing conditions of +8 V/−5 V. The above result is a further demonstration of the good charge storage capability and also confirms the electrical robustness of the thin, interfacial SiO2 layer.

a Hysteresis loop characteristics with voltage shift as large as 1.25 V are observed for both n- and p-MOS capacitors when the gate bias is swept from inversion to accumulation conditions. b I d -V g and c memory endurance characteristics of Ge QD floating gate memories under a +8 V/60 msec pulse programing and a −5 V/30 msec pulse erasing. The I d -V g characteristics are swept from 0 to 2 V. ΔV th of ~0.42 V is achieved with negligible ΔV th degradation following 105 program/erase cycles

Conclusions

We have demonstrated a unique approach for generating self-aligned SiO2/Ge QD/SiO2/SiGe shell MOS heterostructures using a single oxidation step of SiGe nanopillars over a buffer Si3N4 layer on the Si substrate. Further, we have realized Ge QD floating gate memory devices based on this designer heterostructure. Superior interfacial morphologies and high-quality electrical properties of the SiO2/Ge QD/SiO2/SiGe shell heterostructure have been multiply confirmed by extensive TEM, EDX, I-V, and C-V characterization. Thanks to the thin and robust tunneling oxide, charge storage within the Ge QDs produces considerable voltage shifts under relatively low-voltage programing/erasing conditions with good memory endurance characteristics.

Our self-aligned, Ge QD-based, gate-stacking structure is analogous to the prevailing poly-Si/SiO2/Si MOS structure and indeed provides a practically achievable core building block for Ge-based MOS devices with size-tunable Ge gates, SiO2 gate oxide, and SiGe channels. It is worthwhile to point out the electronic performance advantages of the single-crystalline SiGe shell arising both from having superior interface properties as well as being in a state of compressive stress inherently generated during the fabrication process, which are favorable for the production of high-performance p-MOSFETs. Further device structure design including the pillar (or QD) density and gate area is undergoing for the optimal performance of n- and p-MOSFETs. Thus, we believe that our self-aligned heterostructure is a very promising functional candidate for the realization of next-generation, high-performance SiGe (or Ge) MOSFETs, using the precise control available through our self-organized, single-step fabrication process.

References

del Alamo JA. Nanometre-scale electronics with III–V compound semiconductors. Nature. 2011;479:317–23.

Gu JJ, Liu YQ, Wu YQ, Colby R, Gordon RG, Ye PD. First experimental demonstration of gate-all-around III-V MOSFETs by top-down approach. Proc Int Electron Devices Meet. 2011;33(2):1–4. Washington, 5–7 December.

Heyns M, Tsai W. Ultimate scaling of CMOS logic devices with Ge and III–V materials. MRS Bull. 2009;34:485–92.

Doornbos G, Passlack M. Benchmarking of III–V n-MOSFET maturity and feasibility for future CMOS. IEEE Electron Device Lett. 2010;31:1110–2.

del Alamo JA, Antoniadis D, Guo A, Kim DH, Kim TW, Lin J, et al. InGaAs MOSFETs for CMOS: recent advances in process technology. Proc Int Electron Devices Meet. 2013;2(1):1–4. Washington, 9–11 December.

Oktyabrsky S, Nishi Y, Koveshnikov S, Wang WE, Goel N, Tsai W. Materials and technologies for III-V MOSFETs. In: Oktyabrsky S, Ye PD, editors. Fundamentals of III-V semiconductor MOSFETs. Boston: Springer; 2010. p. 195–238.

Gupta S, Chen R, Magyari Kope B, Lin H, Yang B, Nainani A, et al. GeSn technology: extending the Ge electronics roadmap. Proc Int Electron Devices Meet. 2011;16(6):1–4. Washington, 5–7 December.

Brunco DP, De Jaeger B, Eneman G, Mitard J, Hellings G, Satta A, et al. Germanium MOSFET devices: advances in materials understanding, process development, and electrical performance. J Electrochem Soc. 2008;155:H552–61.

Nishimura T, Lee CH, Tabata T, Wang SK, Nagashio K, Kita K, et al. High-electron-mobility Ge n-channel metal-oxide-semiconductor field-effect transistors with high-pressure oxidized Y2O3. Appl Phys Express. 2011;4:064201.

Yu HY, Ishibashi M, Park JH, Kobayashi M, Saraswat KC. p-Channel Ge MOSFET by selectively heteroepitaxially grown Ge on Si. IEEE Electron Device Lett. 2009;30:675–7.

Zhang R, Iwasaki T, Taoka N, Takenaka M, Takagi S. High-mobility Ge pMOSFET with 1-nm EOT A2O3/GeOx/Ge gate stack fabricated by plasma post oxidation. IEEE Trans Electron Devices. 2012;59:335–41.

Wu JH, Li PW. Ge nanocrystal metal-oxide-semiconductor transistors with Ge nanocrystals formed by thermal oxidation of poly-Si0.88Ge0.12. Semicond Sci Technol. 2007;22:S89–92.

Toriumi A, Tabata T, Lee CH, Nishimura T, Kita K, Nagashio K. Opportunities and challenges for Ge CMOS—control of interfacing field on Ge is a key. Microelectron Eng. 2009;86:1571–6.

Lee CH, Nishimura T, Nagashio K, Kita K, Toriumi A. High-electron-mobility Ge/GeO2 n-MOSFETs with two-step oxidation. IEEE Trans Electron Devices. 2011;58:1295–301.

Takenaka M, Zhang R, Takagi S. MOS interface engineering for high-mobility Ge CMOS. Proc IEEE Int Reliabil Phys Symposium. 2013;4C(1):1–8. Anaheim, 14–18 April.

Swaminathan S, Oshima Y, Kelly MA, McIntyre PC. Oxidant prepulsing of Ge (100) prior to atomic layer deposition of Al2O3: in situ surface characterization. Appl Phys Lett. 2009;95:032907.

Chien CY, Chang YJ, Chen KH, Lai WT, George T, Scherer A, et al. Nanoscale, catalytically enhanced local oxidation of silicon-containing layers by ‘burrowing’ Ge quantum dots. Nanotechnology. 2011;22:435602.

Kuo MH, Wang CC, Lai WT, George T, Li PW. Designer Ge quantum dots on Si: a heterostructure configuration with enhanced optoelectronic performance. Appl Phys Lett. 2012;101:223107.

Wang CC, Liao PH, Kuo MH, George T, Li PW. The curious case of exploding quantum dots: anomalous migration and growth behaviors of Ge under Si oxidation. Nanoscale Res Lett. 2013;8:192.

Chen KH, Wang CC, George T, Li PW. The role of Si interstitials in the migration and growth of Ge nanocrystallites under thermal annealing in an oxidizing ambient. Nanoscale Res Lett. 2014;9:339.

Pezzoli F, Bonera E, Grilli E, Guzzi M, Sanguinetti S, Chrastina D, et al. Raman spectroscopy determination of composition and strain in Si1-xGex/Si heterostructures. Mater Sci Semiconductor Proc. 2008;11:279–84.

Liao PH, Hsu TC, Chen KH, Cheng TH, Hsu TM, Wang CC, et al. Size-tunable strain engineering in Ge nanocrystals embedded within SiO2 and Si3N4. Appl Phys Lett. 2014;105:172106.

Weast RC, Lide DR, Astle MJ, Byer WH. CRC handbook of chemistry and physics. 70th ed. Boca Raton: CRC Press; 1989.

Ren J, Li B, Zheng JG, Olmedo M, Zhou H, Shi Y, et al. Nonplanar nisi nanocrystal floating-gate memory based on a triangular-shaped Si nanowire array for extending nanocrystal memory scaling limit. IEEE Electron Device Lett. 2012;33:1390–2.

Whang SJ, Lee KH, Shin DG, Kim BY, Kim MS, Bin JH, et al. Novel 3-dimensional dual control-gate with surrounding floating-gate (DC-SF) NAND flash cell for 1Tb file storage application. Proc Int Electron Devices Meet. 2010;29(7):1–4. 2010 San Francisco 6–8 December.

Zhu X, Li Q, Ioannou DE, Gu D, Bonevich JE, Baumgart H, et al. Fabrication, characterization and simulation of high performance Si nanowire-based non-volatile memory cells. Nanotechnology. 2011;22:254020.

Acknowledgements

This work was supported by the Ministry of Science and Technology of Republic of China (MOST-102-2221-E-009-195-MY3) as well as by the Asian Office of Aero-space Research and Development under contract no. FA 2386-14-1-4008.

Author information

Authors and Affiliations

Corresponding author

Additional information

Competing Interests

The authors declare that they have no competing interests.

Authors’ Contributions

WL conceived the experimental work and contributed to data analysis and the manuscript preparation. KY and TH performed structure/device fabrication and characterization. PHL carried out the Raman examination and analysis. TG conceived the mechanism of heterostructure formation and revised the manuscript. PWL conceived the study, revised the manuscript, and supervised the work. All authors read and approved the final manuscript.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made.

The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

To view a copy of this licence, visit https://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Lai, WT., Yang, KC., Hsu, TC. et al. A Unique Approach to Generate Self-Aligned SiO2/Ge/SiO2/SiGe Gate-Stacking Heterostructures in a Single Fabrication Step. Nanoscale Res Lett 10, 224 (2015). https://doi.org/10.1186/s11671-015-0927-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1186/s11671-015-0927-y