Abstract

Highly powered electrostatic capacitors based on nanostructures with a high aspect ratio are becoming critical for advanced energy storage technology because of their high burst power and energy storage capability. We report the fabrication process and the electrical characteristics of high capacitance density capacitors with three-dimensional solid-state nanocapacitors based on a ZnO nanowire template. Stand-up ZnO nanowires are grown face down on p-type Si substrates coated with a ZnO seed layer using a hydrothermal method. Stacks of AlZnO/Al2O3/AlZnO are then deposited sequentially on the ZnO nanowires using atomic layer deposition. The fabricated capacitor has a high capacitance density up to 92 fF/μm2 at 1 kHz (around ten times that of the planar capacitor without nanowires) and an extremely low leakage current density of 3.4 × 10−8 A/cm2 at 2 V for a 5-nm Al2O3 dielectric. Additionally, the charge-discharge characteristics of the capacitor were investigated, indicating that the resistance-capacitance time constants were 550 ns for both the charging and discharging processes and the time constant was not dependent on the voltage. This reflects good power characteristics of the fabricated capacitors. Therefore, the current work provides an exciting strategy to fabricate low-cost and easily processable, high capacitance density capacitors for energy storage.

Similar content being viewed by others

Background

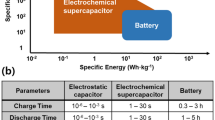

Even after decades of research, energy storage technology continues to be a major challenge for advanced modern society. The development of small size, lightweight, and environmentally friendly energy storage devices has attracted great attention owing to fast-growing energy demands for portable and wearable electronics [1]. Therefore, energy storage systems including fuel cells, batteries, and supercapacitors are being adapted and optimized with nanostructured components [2]. Among various nanostructure-based energy storage devices, nanocapacitor arrays have been extensively studied for the next generation of energy storage systems because of their moderate energy density and high power density [3].

According to the well-known equation for a parallel-plate capacitor, C = ε 0 ε r A/d, where C is the capacitance, ε 0 and ε r are the dielectric constants of the vacuum and dielectric, respectively, A is the surface area of the electrode, and d is the thickness of the dielectric; the capacitance density can be increased by including high-permittivity dielectrics such as Al2O3, HfO2, and TiO2, including various hybrid dielectric stacks to increase ε r and using three-dimensional (3D) capacitor designs to achieve a larger capacitor electrode area to increase A [4]. Decreasing d is not usually an option for capacitors in power applications because this could lead to a higher leakage current and a lower breakdown voltage. Therefore, 3D nanocapacitor arrays with a high aspect ratio are considered to be a robust candidate to achieve a high capacitance density. To date, many methods have been proposed for the fabrication of 3D nanocapacitors, mainly focusing on different nanostructured templates such as anodic aluminum oxide (AAO) [5–11], carbon nanotubes (CNTs) [12, 13], silicon-based nanowires, nanoholes and nanopillars [14–18], and InAs nanowires [19]. The AAO template has been widely used because nanopore arrays exhibit a high degree of regularity and uniformity. However, conventional AAO fabrication needs a relatively long time, the use of resources is inefficient, and the chemicals can be toxic, which restrict their practical application [20]. Although a CNT template has a good electrical conductivity and can be used as capacitor electrodes, the production of CNTs usually needs quite a high growth temperature (>750 °C) [13]. The leakage current characteristics of the CNT-based nanocapacitors are usually unsatisfactory, which is attributed to the top connection of stand-up CNTs when they become long enough, thus resulting in an increase in leakage paths [12]. Silicon-based nanostructures are easily integrated with current silicon technologies. Nevertheless, silicon nanoholes with a high aspect ratio are difficult to etch and the definition of multilayered structure capacitors requires costly lithography processes [16]. The growth of silicon nanowires usually requires a relatively high temperature (>400 °C), which is not suitable for flexible devices [14].

During the past decade, ZnO nanostructures such as nanoparticles, nanorods, nanoforests, and nanowires (NWs) have been investigated intensively for various applications because of their wide bandgap, excellent thermal and chemical stability, and special electrical and optoelectronic characteristics [21–23]. For instance, ZnO nanoforests have been explored for photoelectrochemical applications because of their large surface area [24], and long stand-up ZnO nanowires or nanorods are necessary for piezoelectric devices or solar cells [25, 26]. Nevertheless, there are no reports of using stand-up ZnO NW templates for the fabrication of 3D nanocapacitors. Various synthesis methods of ZnO NWs have been reported such as the vapor-liquid-solid process [27], chemical vapor deposition (CVD) [28], pulse laser deposition [29], and hydrothermal synthesis [30, 31]. Among these growth processes, the hydrothermal synthesis is preferred because of its low cost, low growth temperature, and large growth area and because it is environmentally benign. On the other hand, the selection of electrode materials also plays an important role in the preparation of 3D nanocapacitors. Transparent conducting oxides (TCOs), including indium oxide and aluminum-doped zinc oxide (AZO), have many attractive properties such as good thermal stability, relatively low resistivity, and high transmittance [32, 33]. Introducing TCOs as electrodes of 3D nanocapacitors could make it possible for the integration of energy storage devices and optoelectronic devices.

Therefore, this article reports the preparation of stand-up ZnO nanowires on a silicon substrate using a hydrothermal synthesis. Using the ZnO nanowire as a template and the AZO film as an electrode, high-density 3D solid-state capacitors were fabricated and characterized physically and electrically for energy storage applications.

Methods

The experimental procedure for the fabrication of the ZnO NW-based nanocapacitor arrays is illustrated schematically in Fig. 1. The whole fabrication procedure included six key steps: deposition of a ZnO seed layer, growth of ZnO nanowires, deposition of a thin bottom electrode layer, deposition of a dielectric layer, deposition of a top electrode layer, definition of a top contact layer, and formation of the capacitors. The detailed process steps are described as follows.

Growth of the Stand-Up ZnO Nanowires

ZnO nanowires were synthesized via a modified hydrothermal method, which was described in our previous paper [34]. First, p-type Si wafers were cleaned with the standard Radio Corporation of America (RCA) cleaning process, and then, around 18 nm of a ZnO thin film was grown on the Si substrate at 200 °C using atomic layer deposition (ALD). This was then used as the seed layer of ZnO NWs. Zn(C2H5)2 and deionized water (DI water) were employed as the precursors for the ALD ZnO. Subsequently, the ZnO seed layer-coated Si substrate was transferred into a Teflon-lined stainless steel autoclave filled with aqueous solution consisting of 0.025 M zinc nitrate hexahydrate [Zn(NO3)2·6H2O)] and 0.025 M hexamethylenetetramine (C6H12N4). It is worthwhile emphasizing that the ZnO seed layer should be face down in the solution. The autoclave was sealed tightly and kept in a stove at 80 °C for 8 h. After that, the resulting sample was removed from the solution and thoroughly rinsed with DI water. It was then dried using a slow high-purity nitrogen flow.

Deposition of the Conducting and Insulating Thin Films

First, a 10-nm AZO layer was deposited on the as-grown ZnO NWs using thermal ALD at 200 °C, which served as the bottom electrode layer. Herein, the AZO layer was composed of alternate 20 cycles of ZnO and 1 cycle of Al2O3, giving a resistivity of 1.8 × 10−3 Ω cm. ZnO and Al2O3 were grown from the Zn(C2H5)2/H2O and Al(CH3)3/H2O precursors, respectively. To investigate the effect of dielectric thickness, various thicknesses of Al2O3 layers (5, 10, 15, and 20 nm) were deposited using ALD at 200 °C, acting as the insulator for the nanocapacitors. After the deposition of Al2O3, a 150-nm AZO layer was deposited by ALD for the top electrode. Thus, the AZO/Al2O3/AZO capacitor stack was formed. To ensure full diffusion of the precursor molecules into and the gaseous byproducts out of the gaps among the ZnO NWs, five precursor-pulsing and purging durations were adopted in comparison with those normally used for a flat substrate.

Formation of the Contact and Definition of Capacitors

A 150-nm Mo layer serving as the top contact was deposited using radio frequency magnetron sputtering, and the shape and size of the contact pad were defined using photolithography and a metal lift-off process. Subsequently, the top AZO film outside the pads was etched using dilute hydrochloric acid, and thus, the separated capacitors consisting of nanocapacitors were formed for electrical characterization.

Characterization Methods

The top view and cross-sectional morphologies of the as-grown ZnO NWs and those coated with different thin films were characterized with scanning electron microscopy (SEM) (Zeiss SIGMA HD microscope, Germany). The cross-sectional images of the fabricated capacitors were observed using field-emission TEM (FEI Tecnai G2 F20 S-TWIN) with an accelerating voltage of 200 kV. Capacitance-voltage (C-V) and impedance measurements were carried out on a precision impedance analyzer (4294A; Agilent Technologies, Malaysia). Current-voltage (I-V) was measured on a semiconductor device analyzer (Agilent B1500A; Agilent Technologies, Japan). Charging-discharging characteristics of the capacitors were measured on a function/arbitrary waveform generator (Agilent 33250A; Agilent Technologies, Germany).

Results and Discussion

Figure 2 shows the cross-sectional and top-view SEM images of the as-grown ZnO NWs and those coated with different thin films formed using ALD as well as the fabricated capacitor. As shown in Fig. 2a, the as-grown ZnO NWs on the seed layer of ZnO stand approximately in an upwards direction with a diameter of 20–30 nm and a height of 500–600 nm. The extracted area density of ZnO NWs is close to 7 × 109 cm−2, which is in good agreement with the reported values [23]. ZnO NWs with such a high density and high aspect ratio can guarantee a greatly increased electrode area and hence a significant enhancement in capacitance density. The top view of the ZnO NWs is shown in the inset of Fig. 2a, revealing their high density. After deposition of a 10-nm Al-doped ZnO (AZO) film, the ZnO NWs were coated uniformly with the AZO layer, displaying very smooth surfaces and increased diameters of the NWs, as shown in Fig. 2b. Subsequently, different thicknesses of Al2O3 films were deposited on the NWs, serving as the dielectric of the nanocapacitor, as illustrated in Fig. 2c–f. As the thickness of Al2O3 increased from 5 to 20 nm, the gaps in the NWs were increasingly full. The diameters of the coated NWs showed an increasing trend, clearly demonstrated in the inserts of Fig. 2c–f. After the deposition of a 150 nm AZO layer acting as the top electrode, the NWs were completely covered, as shown in Fig. 2g. The top-view SEM image reveals a rough top surface likely caused by the different heights of the ZnO NWs (see the insert of Fig. 2g). Finally, the fabricated capacitor with a Mo contact pad is shown in Fig. 2h, which actually consists of many nanocapacitors. Although irregular margins of the pad/AZO electrode can be observed in Fig. 2h, which could result from a lateral etching effect and/or the lift-off process, they can be ignored compared with the large area of the electrode.

Cross-sectional SEM images of a the as-grown ZnO nanowires (NWs), b 10-nm AZO-coated ZnO NWs, c–f ZnO NWs surrounded by 10 nm AZO and 5, 10, 15, and 20 nm Al2O3, respectively, g the structures with deposition of 150 nm AZO acting as the top electrode, h the fabricated capacitor with a pad (shown by the dark region), and the area without a pad (shown by the bright region). The insert shows the top view of the corresponding sample at a 50° tilt

Figure 3 shows the cross-sectional transmission electron microscopy (TEM) images of the fabricated capacitors with 5 and 20 nm of Al2O3 dielectric layers, respectively. It was found that each capacitor contains many 3D nanocapacitors based on the stand-up ZnO NW template, as shown in Fig. 3a, b. Additionally, the stand-up NWs are coated uniformly and conform to an Al2O3 dielectric layer, and the thickness of Al2O3 was accurately controlled, as shown in Fig. 3c, d.

Figure 4 shows the typical capacitance density as a function of voltage at 1 kHz for the ZnO NW-based capacitors with an Al2O3 dielectric layer ranging from 5 to 20 nm in comparison with the planar capacitor with a 5-nm Al2O3 dielectric. The C-V curves exhibited a shape typical of metal-insulator-metal capacitors, which was attributed to the metal-like AZO films with resistivity of 1.8 × 10−3 Ω cm. The inset shows a schematic of the electrical test structure, which illustrates that the AZO/Al2O3/AZO multi-layers act as a metal-insulator-metal structure, and the bulk of the ZnO NW/seed layer/Si substrate serves as a series resistor. As the thickness of Al2O3 increased gradually from 5 to 20 nm, the resulting capacitance density decreased. In theory, the capacitance density should increase four times as the thickness of Al2O3 decreases from 20 to 5 nm. However, in terms of the 5 nm Al2O3, a capacitance density as large as 92 fF/μm2 was achieved at zero voltage, which is about ten times that of the planar capacitor with 5 nm of Al2O3, and it is around eight times that (11 fF/μm2) of the 20 nm Al2O3. This deviates seriously from the theoretical value, which can be explained as follows. When the Al2O3 dielectric layer became very thick, the gaps in the NWs were easily filled; thus, the real contact area between the electrode and the dielectric layer decreased. This reduces the capacitance density. However, the theoretical capacitance of the fabricated capacitor was also estimated by considering each capacitor as an array of parallel cylindrical nanocapacitors. For a single nanocapacitor, the capacitance can be approximated by that of a cylindrical capacitor, described in Eq. (1) [35]:

Typical capacitance-voltage (C-V) characteristics of the ZnO NW-based capacitors with different thicknesses of the Al2O3 dielectric at 1 kHz. As a comparison, the C-V curve of the planar capacitor with a 5-nm Al2O3 dielectric is also illustrated. The inset shows the schematic of the electrical test structure

where ε0 is the permittivity in vacuum, ε r is the relative dielectric constant of Al2O3 (ε r = 8.9), h is the average height of the ZnO NWs (h = 550 nm), a is the average diameter of the ZnO NWs coated with the AZO layer (a = 45 nm), and b is the coaxial diameter of the Al2O3 dielectric layer. If the parallel nanocapacitor array is taken into consideration, the total capacitance density is given by Eq. (2):

where the additional factor, d, is the area density of the nanowires. In this case, d = 7 × 109 cm−2. Regarding the 5-nm Al2O3 dielectric layer, b was calculated to be 55 nm; thus, the estimated capacitance density is about 94.9 fF/μm2, which is close to the experimental value of 92 fF/μm2.

To observe the uniformity of the capacitance density of the fabricated capacitors, ten capacitors for each thickness of Al2O3 were randomly selected for C-V measurements at 1 kHz. Figure 5 shows the cumulative distribution characteristics of the capacitance densities for capacitors with 5-, 10-, 15-, and 20-nm Al2O3 layers at 1 kHz and zero voltage. With respect to the 5-nm Al2O3 layer, the resulting capacitance density has a narrow distribution ranging from 85 to 92 fF/μm2; the capacitance density at a 50 % cumulative probability is as large as 89 fF/μm2. As the thickness of Al2O3 increases from 10 to 20 nm, the distribution of the resulting capacitance densities becomes much narrower. This indicates that our fabricated capacitors have quite good electrical uniformity, which relates to the uniform ZnO NWs.

Figure 6 illustrates the leakage current density as a function of voltage for the fabricated capacitors with various thicknesses of Al2O3 at room temperature. The leakage current density (defined as the leakage current/the footprint area) decreases from 3.4 × 10−8 to 3.5 × 10−9 A/cm2 at 2 V as the thickness of Al2O3 increases from 5 to 20 nm. If the real contact area between the Al2O3 dielectric and the AZO electrode (denoted by RA) is taken into account, the resulting leakage current density should be even smaller. For example, for the capacitor with a 5-nm Al2O3 dielectric layer, using the capacitance obtained from the C-V measurements and the equation of a parallel plate capacitor, we extracted a real electrode area of 5.7 × 104 μm2, which is more than five times the footprint area (100 × 100 μm2). Therefore, the real leakage current density was calculated to be 6 × 10−9 A/cm2, which is remarkably superior to most of the reported results. Such a low leakage current density was attributed to the high-quality Al2O3 dielectric and superior interfaces of AZO/Al2O3, which were formed by successive ALD of AZO and Al2O3 layers without breaking the vacuum.

To compare the current work with other reports on nanocapacitors, Table 1 shows the characteristics of various reported nanocapacitors. Banerjee et al. [5] reported the AAO template-based electrostatic nanocapacitors on a glass substrate, which exhibited a very high equivalent planar capacitance density (EPCD) and a small leakage current density. However, the corresponding capacitance was measured at a frequency as low as 20 Hz. As the authors mentioned, their capacitors showed noticeable capacitance dispersion when the measurement frequency was higher than 100 Hz, thus leading to a decrease in capacitance [5]. Both the transfer and bonding of the AAO template onto other substrates are time-consuming and delicate operations. Klootwijk et al. [16] demonstrated an EPCD of 440 fF/μm2 using ALD multiple layers of TiN/Al2O3 inside silicon trenches. The fabricated capacitor exhibited a relatively high leakage current density. However, the fabrication of this type of nanocapacitor needs multiple lithography and etching steps, especially for the reactive ion etching process for the Si trenches with a high aspect ratio. These definitely increase the fabrication cost. Although Morel et al. [14] reported Si nanowire-based nanocapacitors with an EPCD of 180 fF/μm2, the leakage current density was not satisfactory. This is likely because of the diffusion of the copper catalyst incorporated in the growth of the Si nanowires. It also needed a relatively high temperature (425 °C) for the growth of the Si NWs. Briefly, compared with other nanocapacitors based on various templates, our capacitor with 5 nm of Al2O3 has a high EPCD up to 92 fF/μm2 and an extremely low leakage current density of 3.4 × 10−8 A/cm2 at 2 V. Most importantly, easily processable ZnO NWs were adopted as a template for our nanocapacitors, which have some advantages such as the low cost, easy scale up, and low thermal budget. Furthermore, by increasing the aspect ratio of ZnO NWs and/or using an insulator with a higher dielectric constant, the EPCD can be further enhanced.

According to the charge and discharge processes of the resistor-capacitor circuits, the charge-discharge rate of the capacitor and hence the power characteristics of the capacitors are determined by the resistance-capacitance (RC) time constant [36]. The RC time constant (τ) is defined as the duration when the circuit current comes to e−1 (36.8 %) of the initial value. Figure 7a shows the charge-discharge curve of the fabricated capacitor with a 5-nm Al2O3 film and the equivalent RC circuit. The time constant is defined by τ c and τ d in the charging and discharging processes, respectively. When a 1 V bias is applied to the top electrode, both τ c and τ d are approximately equal to 550 ns; such short time constants are in accordance with the power characteristics of the electrostatic capacitor. The impedance analysis was carried out to estimate the internal resistance of the nanocapacitors, and the obtained impedance spectrum is shown in Fig. 7b. The curve shows a very steep behavior in the low frequency region, revealing good capacitor characteristics. The inset shows a magnified view of the impedance spectrum in the high frequency region, and the intercept at the real part axis indicates an equivalent series resistance (ESR) of the capacitor, revealing an ESR of about 110 Ω. Then, taking the load resistance (R L = 50 Ω) and capacitance into consideration, the time constant was estimated to be 590 ns, which is close to the measurement result. Figure 7c shows the relationship between the charging current and time under different voltage supplies, where V S1 = 1 V, V S2 = 0.8 V, and V S3 = 0.6 V and the resulting time constants τ 1, τ 2, and τ 3 are 550 ns. The results reveal that the time constant has nothing to do with the voltage supply, which is in agreement with the RC charge-discharge theory. The fabricated capacitors could obtain a high capacitance density, without sacrificing the power characteristics of the electrostatic capacitor.

a Charge-discharge curve of the fabricated capacitor with 5 nm of Al2O3 together with the equivalent RC circuit. b Impedance spectrum of the capacitor, which was measured at a dc bias of 0 V with an AC signal of 5 mV over a frequency range from 1 MHz to 1 kHz. c The charging process of the corresponding fabricated capacitor with different voltages. The used pad area is 200 × 200 μm2

Conclusions

In summary, high-density 3D solid-state nanocapacitors based on stand-up ZnO NWs were fabricated successfully for the first time. For a 5-nm Al2O3 insulator, the capacitor had a high EPCD of up to 92 fF/μm2, an extremely low leakage current density of 3.4 × 10−8 A/cm2 at 2 V, and an RC time constant of 550 ns. These data reveal that the fabricated nanocapacitors have a high capacitance density, good power characteristics, and a low power consumption. In particular, such a low leakage current density means that the current nanocapacitor structure is very promising for energy storage applications. All the fabrication steps were carried out with a maximum processing temperature of 200 °C; thus, this can facilitate the manufacture of nanocapacitors on flexible substrates.

References

Aricò AS, Bruce P, Scrosati B, Tarascon J-M, Schalkwijk WV (2005) Nanostructured materials for advanced energy conversion and storage devices. Nat Mater 4:366–377

Futaba DN, Hata K, Yamada T, Hiraoka T, Hayamizu Y, Kakudate Y et al (2006) Shape-engineerable and highly densely packed single-walled carbon nanotubes and their application as super-capacitor electrodes. Nat Mater 5:987–994

Sherrill SA, Banerjee P, Rubloff GW, Lee SB (2011) High to ultra-high power electrical energy storage. Phys Chem Chem Phys 13:20714–20723

Han HC, Chong CW, Wang SB, Heh D, Tseng CA, Huang YF et al (2013) High K nanophase zinc oxide on biomimetic silicon nanotip array as supercapacitors. Nano Lett 13:1422–1428

Banerjee P, Perez I, Henn-Lecordier L, Lee SB, Rubloff GW (2009) Nanotubular metal–insulator–metal capacitor arrays for energy storage. Nat Nanotchnol 4:292–296

Sohn JI, Kim Y, Nam C, Cho BK, Seong T, Lee S (2005) Fabrication of high-density arrays of individually isolated nanocapacitors using anodic aluminum oxide templates and carbon nanotubes. Appl Phys Lett 87:123115

Haspert LC, Lee SB, Rubloff GW (2012) Nanoengineering strategies for metal-insulator-metal electrostatic nanocapacitors. ACS Nano 6:3528–3536

Zhang GZ, Wu H, Chen C, Wang T, Wu WH, Yue J et al (2015) Transparent nanotubular capacitors based on transplanted anodic aluminum oxide templates. ACS Appl Mater Interfaces 7:5522–5527

Li LJ, Zhu B, Ding SJ, Lu HL, Sun QQ, Jiang AQ et al (2012) Three-dimensional AlZnO/Al2O3/AlZnO nanocapacitor arrays on Si substrate for energy storage. Nanoscale Res Lett 7:544

Shelimov KB, Davydov DN, Moskovits M (2000) Template-grown high-density nanocapacitor arrays. Appl Phys Lett 77:1722

Han FM, Meng GW, Zhou F, Song L, Li XH, Hu XY et al (2015) Dielectric capacitors with three-dimensional nanoscale interdigital electrodes for energy storage. Sci Adv 1:e1500605

Jang JE, Cha SN, Choi Y, Amaratunga GAJ, Kang DJ, Hasko DG et al (2005) Nanoscale capacitors based on metal-insulator-carbon nanotube-metal structures. Appl Phys Lett 87:263103

Pint CL, Nicholas NW, Xu S, Sun ZZ, Tour JM, Schmidt HK et al (2011) Three dimensional solid-state supercapacitors from aligned single-walled carbon nanotube array templates. Carbon 49:4890–4897

Morel PH, Haberfehlner G, Lafond D, Audoit G, Jousseaume V, Leroux C et al (2012) Ultra high density three dimensional capacitors based on Si nanowires array grown on a metal layer. Appl Phys Lett 101:083110

Lehmann V, Nlein WH, Reisinger H, Spitzer A, Wendt H, Willer J (1996) A novel capacitor technology based on porous silicon. Thin Solid Films 276:138–142

Klootwijk JH, Jinesh KB, Dekkers W, Verhoeven JF, van den Heuvel FC, Kim HD et al (2008) Ultrahigh capacitance density for multiple ALD-grown MIM capacitor stacks in 3-D silicon. IEEE Electr Device L 29:740–742

Chang SW, Oh J, Boles ST, Thompson CV (2010) Fabrication of silicon nanopillar-based nanocapacitor arrays. Appl Phys Lett 96:153108

Kemell M, Ritala M, Leskela M, Ossei-Wusu E, Carstensen J, Foll H (2007) Si/Al2O3/ZnO:Al capacitor arrays formed in electrochemically etched porous Si by atomic layer deposition. Microelectron Eng 84:313–318

Roddaro S, Nilsson K, Astromskas G, Samuelson L, Wernersson LE, Karlstrom O et al (2008) InAs nanowire metal-oxide-semiconductor capacitors. Appl Phys Lett 92:253509

Hong YK, Kim BH, Il Kim D, Park DH, Joo J (2015) High-yield and environment-minded fabrication of nanoporous anodic aluminum oxide templates. RSC Adv 5:26872–26877

Vayssieres L (2003) Growth of arrayed nanorods and nanowires of ZnO from aqueous solutions. Adv Mater 15:464–466

Greene LE, Law M, Tan DH, Montano M, Goldberger J, Somorjai G et al (2005) General route to vertical ZnO nanowire arrays using textured ZnO seeds. Nano Lett 5:1231–1236

Song JJ, Lim SW (2007) Effect of seed layer on the growth of ZnO nanorods. J Phys Chem C 111:596–600

Sun X, Li Q, Jiang JC, Mao YB (2014) Morphology-tunable synthesis of ZnO nanoforest and its photoelectrochemical performance. Nanoscale 6:8769

Riaz M, Song JH, Nur O, Wang ZL, Willander M (2011) Study of the piezoelectric power generation of ZnO nanowire arrays grown by different methods. Adv Funct Mater 21:628–633

Baxter JB, Walker AM, van Ommering K, Aydil ES (2006) Synthesis and characterization of ZnO nanowires and their integration into dye-sensitized solar cells. Nanotechnology 17:S304–S312

Shi J, Hong H, Ding Y, Yang YA, Wang F, Cai WB et al (2011) Evolution of zinc oxide nanostructures through kinetics control. J Mater Chem 21:9000–9008

Song HS, Zhang WJ, Cheng C, Tang YB, Luo LB, Chen X et al (2011) Controllable fabrication of three-dimensional radial ZnO nanowire/silicon microrod hybrid architectures. Cryst Growth Des 11:147–153

Sun Y, Fuge GM, Ashfold MNR (2004) Growth of aligned ZnO nanorod arrays by catalyst-free pulsed laser deposition methods. Chem Phys Lett 396:21–26

Kozhummal R, Yang Y, Guder F, Hartel A, Lu XL, Kucukbayrak UM et al (2012) Homoepitaxial branching: an unusual polymorph of zinc oxide derived from seeded solution growth. ACS Nano 6:7133–7141

Cheng CW, Liu B, Yang HY, Zhou WW, Sun L, Chen R et al (2009) Hierarchical assembly of ZnO nanostructures on SnO2 backbone nanowires: low-temperature hydrothermal preparation and optical properties. ACS Nano 3:3069–3076

Maeng WJ, Lee JW, Lee JH, Chung KB, Park JS (2011) Studies on optical, structural and electrical properties of atomic layer deposited Al-doped ZnO thin fims with various Al concentrations and deposition temperatures. J Phys D : Appl Phys 44:445305

Maeng WJ, Choi DW, Chung KB, Koh WY, Kim GY, Choi SY et al (2014) Highly conducting, transparent, and flexible indium oxide thin film prepared by atomic layer deposition using a new liquid precursor Et2InN(SiMe3)2. ACS Appl Mater Interfaces 6:17481–17488

Zhang Y, Lu HL, Wang T, Ren QH, Gu YZ, Li DH et al (2015) Facile synthesis and enhanced luminescent properties of ZnO/HfO2 core-shell nanowires. Nanoscale 7:15462–15468

Martel R, Schmidt T, Shea HR, Hertel T, Avouris P (1998) Single- and multi-wall carbon nanotube field-effect transistors. Appl Phys Lett 73:2447–2449

Conway BE (1999) Electrochemical supercapacitors: scientific fundamentals and technological applications. Springer, New York

Acknowledgements

The authors thank the financial support of the National Natural Science Foundation of China (Grant Nos. 61274088, 61474027) and the Research Fund for the Doctoral Program of Higher Education of China (Grant No. 20120071110033).

Author information

Authors and Affiliations

Corresponding author

Additional information

Competing Interests

The authors declare that they have no competing interests.

Authors’ Contributions

LW carried out the main part of fabrication and analytical works. QXL, BZ, and SJD participated in the sequence alignment and drafted the manuscript. WJL, HLL, AQJ, and DWZ conceived the study and participated in its design. All authors read and approved the final manuscript.

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

Wei, L., Liu, QX., Zhu, B. et al. Low-Cost and High-Productivity Three-Dimensional Nanocapacitors Based on Stand-Up ZnO Nanowires for Energy Storage. Nanoscale Res Lett 11, 213 (2016). https://doi.org/10.1186/s11671-016-1429-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1186/s11671-016-1429-2